# DISSERTATION

submitted to the Combined Faculty of Mathematics, Engineering and Natural Sciences of the Ruperto Carola University of Heidelberg, Germany for the degree of Doctor of Natural Sciences

> put forward by **Daniel Alexander Berninghoff** born in Lüdenscheid *Oral examination: 25.05.2022*

# Commissioning of the Front-End Electronics of the LHCb Scintillating Fibre Tracker

Referees: Prof. Dr. Ulrich Uwer Prof. Dr. Klaus Reygers

## Abstract

Between 2019 and 2022, the LHCb experiment has undergone a major upgrade. It enables the detector to be operated at an increased luminosity and to be read out at 40 MHz corresponding to the proton bunch crossing rate at the LHC. In the course of the upgrade, the tracking stations downstream of the magnet have been replaced by a tracker made of scintillating fibres. With a fibre diameter of  $250 \,\mu\text{m}$ , silicon photomultiplier readout and custom front-end electronics, it is well suited for the conditions of the next data taking period.

The front-end electronics of the Scintillating Fibre (SciFi) Tracker follow a modular design and have been optimised for the detector readout at 40 MHz. Before being installed in the upgraded LHCb experiment, every component is thoroughly tested as part of a detailed commissioning procedure. This thesis describes the process of the commissioning and presents the results of a large fraction of the detector. Along with further performance studies, it could be shown that even on large scales the SciFi front-end electronics meets very high quality standards.

## Kurzfassung

In den Jahren zwischen 2019 und 2022 wurde das LHCb Experiment einem umfassenden Upgrade unterzogen. Dieses ermöglicht den Betrieb des Detektors bei erhöhter Luminosität, sowie die Auslesung der Daten bei einer Rate von 40 MHz, was der Protonkollisionsrate am LHC entspricht. Im Zuge des Upgrades wurden die Hauptspurkammern hinter dem Magneten mit einem neuen Detektor ersetzt, der auf szintillierenden Fasern basiert. Mit einem Faserdurchmesser von 250 µm und einer Auslese mittels Silizium Photovervielfachern und maßgeschneideter Elektronik ist der Detektor gut für die neuen Bedingungen gerüstet.

Die Ausleseelektronik des Scintillating Fibre (SciFi) Trackers ist modular aufgebaut und wurde speziell für die Ausleserate von 40 MHz entwickelt. Vor dem Einbau im LHCb Experiment im Zuge des Upgrades wird jede Komponente in einem detaillierten Inbetriebnahmeverfahren sorgfältig getestet. Diese Prozedur wird im Rahmen dieser Arbeit besprochen, sowie die Testergebnisse eines Großteils des Detektors vorgestellt. Zusammen mit weiterführenden Studien konnte gezeigt werden, dass die Ausleseelektronik des SciFi Trackers auch in großen Stückzahlen sehr hohen Qualitätsanforderungen genügt.

# Contents

| 1 | Intro                                                              | ntroduction 1                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                |  |  |  |

|---|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 2 | <b>The</b> 2.1 2.2 2.3 2.4                                         | LHCb Experiment at the LHC         Detector Upgrade         Tracking System         Output         Particle Identification         Trigger and Data Acquisition                                                                                                                                                               | <b>3</b><br>4<br>6<br>9<br>11                                                                                                                                                                  |  |  |  |

| 3 | The<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9 | Motivation for the Tracker UpgradePerformance RequirementsDetector Design and Operating PrincipleScintillating FibresFibre ModulesSilicon PhotomultipliersFront-End ElectronicsInfrastructure3.8.1Electrical Power3.8.2Cooling3.8.3Mechanical Support Structure                                                               | <b>13</b><br>13<br>14<br>15<br>16<br>17<br>24<br>30<br>31<br>32<br>33<br>35<br>36                                                                                                              |  |  |  |

| 4 | From<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6                     | PACIFIC BoardPACIFIC ASIC4.2.1Signal Processing and Digitisation4.2.2Serialisation4.2.3Slow Control Interface and Configuration Registers4.2.4Threshold ScanCluster BoardImage: Cluster SCA4.3.1Cluster SCA4.3.2Cluster FPGAMaster BoardImage: Cluster SCA4.4.1Master GBTX4.4.2Master SCA4.4.3Data GBTXLight Injection System | <ol> <li>39</li> <li>39</li> <li>41</li> <li>42</li> <li>48</li> <li>49</li> <li>50</li> <li>52</li> <li>53</li> <li>54</li> <li>59</li> <li>61</li> <li>62</li> <li>63</li> <li>65</li> </ol> |  |  |  |

| 5  | Com            | missioning of the SciFi Front-End Electronics                                                               | 69       |  |  |  |  |

|----|----------------|-------------------------------------------------------------------------------------------------------------|----------|--|--|--|--|

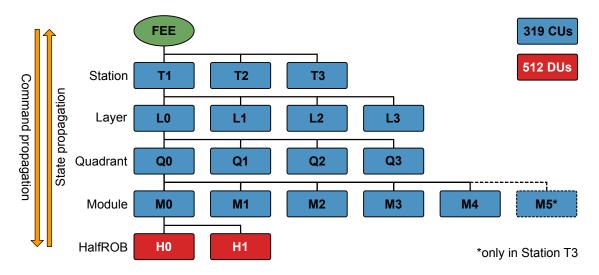

|    | 5.1            | Complexity of Readout System                                                                                | 70       |  |  |  |  |

|    | 5.2            | Front-End Tester                                                                                            | 72       |  |  |  |  |

|    | 5.3            | Commissioning Setup                                                                                         | 73       |  |  |  |  |

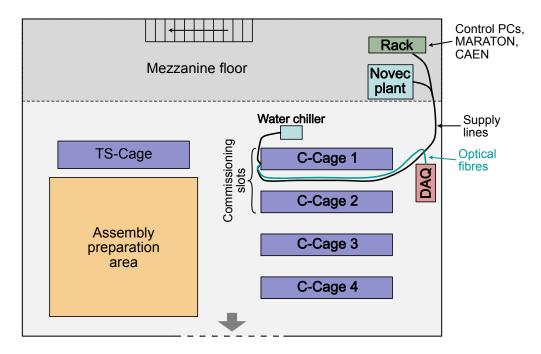

|    |                | 5.3.1 Infrastructure                                                                                        | 75       |  |  |  |  |

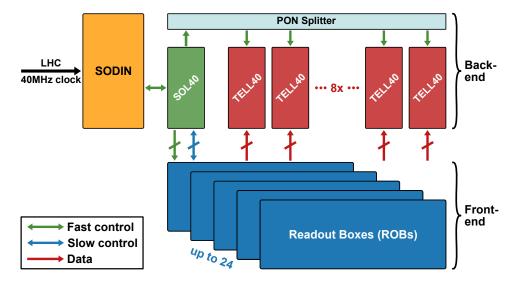

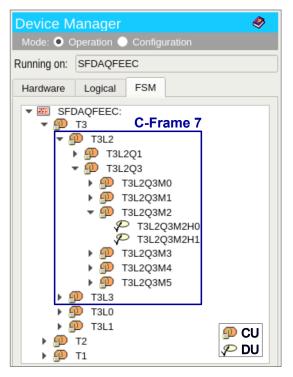

|    |                | 5.3.2 DAQ System                                                                                            | 76       |  |  |  |  |

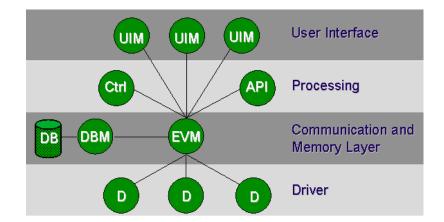

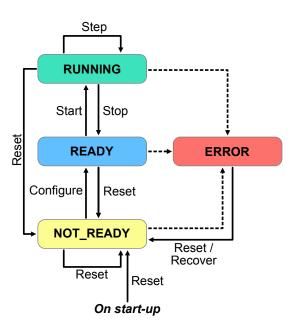

|    |                | 5.3.3 Control Software                                                                                      | 78       |  |  |  |  |

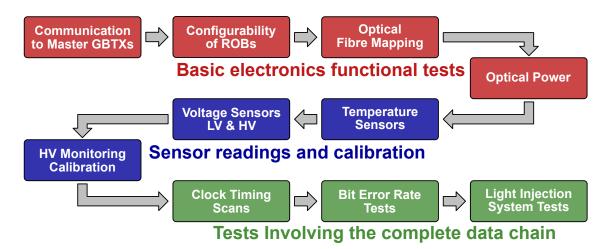

|    |                | 5.3.4 Commissioning Procedure                                                                               | 82       |  |  |  |  |

|    | 5.4            | Communication to Master GBTXs                                                                               | 83       |  |  |  |  |

|    | 5.5            | Configurability of ROBs                                                                                     | 84       |  |  |  |  |

|    | 5.6            | Optical Fibre Mapping                                                                                       | 88       |  |  |  |  |

|    | 5.7            | Optical Power                                                                                               | 89       |  |  |  |  |

|    | 5.8            | Temperature Sensors                                                                                         | 92       |  |  |  |  |

|    | 5.9            | Voltage Sensors                                                                                             | 92<br>96 |  |  |  |  |

|    | 0.9            | 5.9.1 Low Voltage                                                                                           | 90<br>96 |  |  |  |  |

|    |                | 0                                                                                                           | 90<br>97 |  |  |  |  |

|    | F 10           | 5.9.2 High Voltage                                                                                          |          |  |  |  |  |

|    |                | High Voltage Monitoring Calibration                                                                         | 98<br>00 |  |  |  |  |

|    |                | Bit Error Rate Tests                                                                                        |          |  |  |  |  |

|    | 5.12           | Clock Timing Scans                                                                                          |          |  |  |  |  |

|    |                | 5.12.1 FPGA Serialiser $\rightarrow$ Data GBTX (A) $\ldots \ldots \ldots \ldots$                            |          |  |  |  |  |

|    |                | 5.12.2 FPGA Clustering $\rightarrow$ Serialiser (B)                                                         |          |  |  |  |  |

|    |                | 5.12.3 FPGA Deserialiser $\rightarrow$ Clustering (C) $\ldots \ldots \ldots \ldots \ldots$                  |          |  |  |  |  |

|    |                | 5.12.4 PACIFIC $\rightarrow$ FPGA Deserialiser (D) $\ldots \ldots \ldots \ldots \ldots$                     |          |  |  |  |  |

|    |                | 5.12.5 SYNC Pulse $\rightarrow$ PACIFIC (E)                                                                 |          |  |  |  |  |

|    |                | 5.12.6 Conclusion $\ldots$ | 111      |  |  |  |  |

|    | 5.13           | Light Injection System Tests                                                                                | 111      |  |  |  |  |

|    |                | 5.13.1 Functional Test and Mapping                                                                          | 112      |  |  |  |  |

|    |                | 5.13.2 Delay Scan (Lite) $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                     | 113      |  |  |  |  |

|    |                | 5.13.3 Threshold Scans                                                                                      |          |  |  |  |  |

|    | 5.14           | Commissioning Summary                                                                                       |          |  |  |  |  |

|    |                |                                                                                                             |          |  |  |  |  |

| 6  | Perf           |                                                                                                             | 121      |  |  |  |  |

|    | 6.1            | PACIFIC Pulse Height Digitisation                                                                           | 121      |  |  |  |  |

|    |                | 6.1.1 Pedestal Stability                                                                                    | 121      |  |  |  |  |

|    |                | 6.1.2 Internal Charge Injection                                                                             | 123      |  |  |  |  |

|    |                | 6.1.3 Integrator Differences                                                                                | 124      |  |  |  |  |

|    |                | 6.1.4 Comparator Differences                                                                                |          |  |  |  |  |

|    | 6.2            | Clock Distribution                                                                                          | 129      |  |  |  |  |

|    | 6.3            | Dark Count Rate                                                                                             | 131      |  |  |  |  |

| 7  | Con            | clusion                                                                                                     | 133      |  |  |  |  |

| Bi | Bibliography 1 |                                                                                                             |          |  |  |  |  |

## 1 Introduction

The Standard Model (SM) of particle physics [1]–[3] is a well tested and very successful theory that explains the structure of matter and the interactions between the elementary particles. According to the SM, all visible forms of matter are composed of 12 fundamental particles, which are divided into the groups of quarks and leptons. Furthermore, it includes the gauge bosons that are the mediators of the interactions between these particles. One of them is the well-known photon, which is the force carrier of the electromagnetic force. Together with the strong and weak interaction, they represent the three fundamental forces included in the model. Lastly, there is the Higgs boson, which was predicted by Peter Higgs in 1964 [4]. The associated Higgs field plays an important role in the SM, as it explains how the elementary particles gain their masses.

While almost any experimental observation in the field of particle physics is in agreement with the SM predictions, it is not a complete theory. This can already be seen from the fact that the gravitational force, although negligible at the subatomic scale, is not covered by it. Other observations that cannot be explained by the SM are the asymmetry between matter and antimatter in the universe [5], the existence of dark matter [6], and the measurement of neutrino oscillations [7]. It is therefore essential to continue the thorough testing of the SM, as well as theories beyond it.

In 2012, with the observation of the Higgs boson at the Large Hadron Collider (LHC), the last missing elementary particle of the SM was discovered [8], [9]. The LHC near Geneva, Switzerland, is the most powerful particle accelerator in the world. By colliding high-energy protons at enormous intensities, it provides the ideal conditions to probe the SM and search for new physics phenomena.

The LHCb experiment is one of four major experiments that are located at the LHC. It is a dedicated experiment specialised in studying hadrons<sup>1</sup> containing b and c quarks. They are produced in the proton-proton collisions and decay again after a short time into other particles, which can be detected in the experiment. During the first years of operation starting from 2010, the LHCb experiment has recorded the world's largest samples of events containing b and c hadrons [10].

The collected samples allowed for performing important measurements in the field of flavour physics such as the observation of the rare decay  $B_s^0 \to \mu^+ \mu^-$  [11], the determination of the CKM<sup>2</sup> angle  $\gamma$  [12] or the test of lepton universality [13]. While the latter already revealed a slight tension compared to the SM prediction, the

<sup>&</sup>lt;sup>1</sup>Hadrons are composite particles made of two or more quarks that are bound by the strong interaction. They are further divided into mesons (usually containing two quarks) and baryons (usually three quarks).

<sup>&</sup>lt;sup>2</sup>The Cabibbo–Kobayashi–Maskawa (CKM) matrix parametrises the relative weak coupling strengths between the different quark flavours.

#### 1 Introduction

significance of the measurement is statistically limited. In fact, many key results at LHCb are limited by the statistical sensitivity of the data samples. Therefore, to be competitive with the uncertainties of the theoretical predictions, the LHCb experiment will collect data at five times the previous luminosities<sup>1</sup> starting from the middle of the year 2022. In order to prepare the detector for the increasing rates, a three-year upgrade period was required during which in particular the tracking system has been improved.

An essential component of the upgraded tracking system is a detector made of scintillating fibres: the LHCb Scintillating Fibre (SciFi) Tracker. With a fibre diameter of 250 µm, it provides sufficient granularity for the higher number of particle tracks in each event. The produced scintillation light is detected by arrays of silicon photomultipliers (SiPMs), whose output signals are processed and digitised by a complex chain of front-end electronics. The electronics is designed and optimised to sample the signals at a rate of 40 MHz, matching the proton bunch collision rate at the LHC. While the initial version of the LHCb experiment was only read out at a fraction of that rate, the so-called trigger-less readout is required to fully exploit the increase in luminosity.

In the context of this thesis, several contributions to the SciFi Tracker, in particular to the front-end electronics, have been made. While supporting various steps in the research and production phase of the different electronic components, the main responsibility was the initial commissioning of the electronics on a large scale alongside the surrounding infrastructure and the upgraded LHCb DAQ system. A major challenge that had to be overcame in this context was the establishment of the 40 MHz readout of the complex detector. In its final configuration, the SciFi Tracker will produce data volumes up to 20 Tbit/s corresponding to about 40 % of the entire LHCb experiment.

As part of the front-end electronics commissioning, a detailed test procedure has been defined, developed and implemented. In the process, every component is thoroughly tested and validated in its final environment before being released for installation in the experiment. This also includes first calibration and tuning steps that are required for the proper operation of the detector.

The following contents will be discussed in the course of this thesis: In Chapter 2, the LHCb experiment is further introduced, followed by the SciFi Tracker in Chapter 3. Afterwards, in Chapter 4, a detailed overview on the SciFi front-end electronics is given, providing a first complete reference of all components involved. In Chapter 5, the commissioning procedure is presented and the results from the commissioning of a large fraction of the detector are shown. Finally, performance studies that were conducted alongside the commissioning are discussed in Chapter 6.

<sup>&</sup>lt;sup>1</sup>At particle colliders, the luminosity  $\mathcal{L}$  is a measure for the interaction rate  $\dot{N}$  relative to the cross-section  $\sigma$ .

## 2 The LHCb Experiment at the LHC

This chapter aims at introducing the LHCb experiment at the Large Hadron Collider (LHC). The LHC is the largest circular particle accelerator and collider in the world and is located near Geneva, Switzerland. With a circumference of about 27 km, it is placed in a tunnel between 45 m and 170 m below the surface and is operated by the European Organization for Nuclear Research (CERN) as part of a larger accelerator complex [14].

The LHC is designed to collide two proton beams at centre-of-mass energies up to 14 TeV. The high-energy beams are guided around the accelerator ring by superconducting magnets, which are cooled below 2 K using superfluid helium. The beams consist of bunches spaced 25 ns apart, each containing about  $10^{11}$  protons. They travel in opposite directions in two separate beam pipes and are brought to collision at four different points along the ring, resulting in a maximum bunch crossing rate of 40 MHz and an instantaneous luminosity of up to  $10^{34}$  cm<sup>-2</sup> s<sup>-1</sup>. However, several gaps are foreseen in the filling scheme to allow for reliable dumping of the beams, reducing the average collision rate to about 30 MHz [14].

The four major experiments ATLAS, CMS, ALICE and LHCb are placed around the interaction points to study the collisions. ATLAS [15] and CMS [16] are the largest of the four and are designed as multi-purpose detectors covering a broad physics spectrum. By making use of the high luminosity provided by the LHC, the data collected at ATLAS and CMS led to the discovery of a new particle in 2012 [8], [9], whose properties were later found to be in agreement with the Higgs boson in the Standard Model [4], [17]. ALICE is a general-purpose detector focusing on the physics of strongly interacting matter and the quark-gluon plasma [18]. To allow for this, the LHC is designed to be able to also accelerate and collide heavy (Pb) ions at centre-of-mass energies up to 1.15 PeV [14]. While ALICE is specialised in studying these collisions, the other experiments make use of the data collected during heavy ion runs as well.

This also includes the LHCb experiment that is dedicated to study rare decays of hadrons containing b and c quarks as well as performing precision measurements of CP violation [19]. The experiment is located in a cavern 100 m below the surface at the border between France and Switzerland near the airport of Geneva.

#### **Detector Design**

The LHCb detector is designed as a single-arm forward spectrometer covering an angle between 10 mrad and 300 mrad (250 mrad) in the bending (non-bending) plane

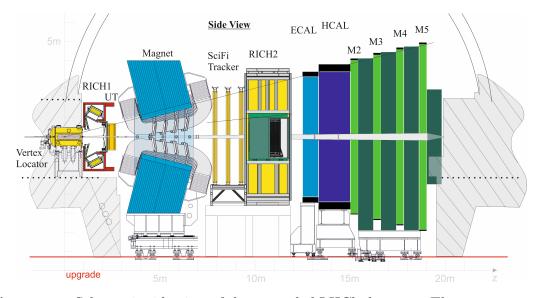

Figure 2.1: Schematic side view of the upgraded LHCb detector. The proton-proton collisions take place inside the Vertex Locator on the left. Image taken from Ref. [20].

of the dipole magnet [19]. This corresponds to a pseudorapidity<sup>1</sup> range  $2 < \eta < 5$ and accounts for about 4% of the solid angle. As illustrated in Fig. 2.1, a righthanded coordinate system is adopted at LHCb, whose z-axis runs horizontally in the direction of the beam pipe. The other horizontal axis (x) is the direction in which charged particles are mainly bent when passing through the magnetic field.

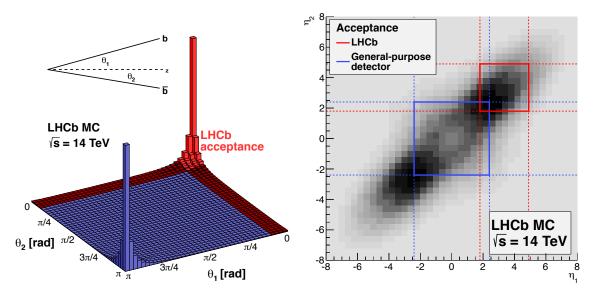

Unlike the three general-purpose detectors at the LHC (ATLAS, CMS and ALICE), which are built in a cylindrical shape around the interaction point in order to achieve a large geometric coverage, the special design of the LHCb detector was chosen specifically for its field of application: As shown in the simulations in Fig. 2.2, the  $b\bar{b}$  quark pairs that are of particular interest at LHCb are predominantly produced at small opening angles to the beam axis, which is reflected in the geometry of the detector.

Between 2019 and 2022, the detector has undergone a major upgrade in order to boost the future data collection rates and thus significantly reduce the statistical uncertainties of the measurements. In the following, the upgraded LHCb experiment as well as the scope of the upgrade are presented.

## 2.1 Detector Upgrade

During the first years of operation between 2010 and 2018, the (initial) LHCb detector recorded data corresponding to an integrated luminosity of about  $9 \,\mathrm{fb}^{-1}$ . Towards the end of this period, the detector was operating at a centre-of-mass energy  $\sqrt{s} = 13 \,\mathrm{TeV}$  and an instantaneous luminosity  $\mathcal{L} = 4 \cdot 10^{32} \,\mathrm{cm}^{-2} \,\mathrm{s}^{-1}$  [22]. It

<sup>&</sup>lt;sup>1</sup>The pseudorapidity  $\eta$  is related to the angle to the beam pipe  $\theta$  via the equation  $\eta = -\ln[\tan(\theta/2)].$

Figure 2.2: Simulated  $b\bar{b}$  production angles at centre-of-mass energies  $\sqrt{s} = 14 \text{ TeV}$  as a function of the angles  $\theta_{1,2}$  (left) and pseudorapidities  $\eta_{1,2}$  (right). The LHCb acceptance is highlighted in red and is compared with typical values for a general-purpose detector in case of the pseudorapidities. Images modified from Ref. [21].

should be noted that this value is about two orders of magnitudes below the LHC design luminosity. With the help of a tunable beam focus and separation at its interaction point, LHCb is able to lower the luminosity to an optimal level for the experiment [19]. This procedure is performed in order to limit the number of visible proton-proton interactions per bunch crossing, which is required for a clean and efficient event reconstruction.

Starting from LHC Run 3 in 2022, the LHCb detector will be operated at five times the luminosity compared to before the upgrade. Until the end of Run 4, this corresponds to a collected data volume of  $50 \, \text{fb}^{-1}$  [23]. This results in a significant reduction of statistical uncertainties and allows the experiment to reach its full flavour-physics potential at the LHC. However, several improvements need to be made during the upgrade prior to Run 3 in order to prepare the detector for the larger number of proton-proton interactions and track multiplicities.

This concerns in particular the LHCb tracking system, which is completely replaced during the upgrade between 2019 and 2022. Furthermore, the trigger system undergoes a fundamental change. In the initial version, the readout of the detector was performed at 1 MHz as determined by the first trigger level implemented in hardware [19]. While the so-called L0 trigger provides high efficiencies for dimuon events, it quickly saturates for hadronic channels [23]. To fully profit from the increase in luminosity, it was decided to perform a trigger-less readout of the complete detector at the 40 MHz bunch crossing rate. To achieve this, it is required that the front-end electronics of all sub-systems are revised and replaced.

In the following, an overview of the various sub-systems of the upgraded LHCb

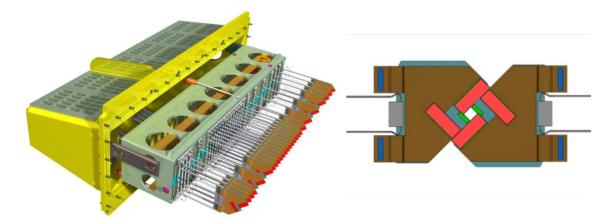

**Figure 2.3:** Schematic view of one half of the upgraded LHCb Vertex Locator (VELO) consisting of 26 modules (left). Two opposing modules from both halves in the closed position are shown on the right. Image adapted from Ref. [26].

detector is given.

## 2.2 Tracking System

As previously discussed, the tracking system undergoes major changes during the LHCb upgrade as it is completely replaced by new detectors. The system is responsible for reconstructing the trajectories of charged particles. It consists of three parts that are located closely around the interaction point in order to resolve production and decay vertices, as well as before and after the dipole magnet. By measuring the deflection angle of charged particles caused by the Lorentz force in the magnetic field, this arrangement enables the determination of the particles' momenta.

### Vertex Locator (VELO)

The (upgraded) LHCb Vertex Locator (VELO) is a silicon pixel detector that is placed closely around the proton-proton interaction region. It consists of two detector halves equipped with 26 modules each. The modules are arranged along the beam axis and are oriented perpendicular to the beam. The detector consists of a total of about 41M pixels with a size of  $55 \times 55 \,\mu\text{m}^2$  [24]. They are grouped in four silicon hybrid pixel tiles per module, whereas each tile is readout by three VeloPix ASICs. The total output data rate is estimated at 1.6 Tbit/s while reading out the front-end electronics at the full LHC bunch crossing rate of 40 MHz [25].

A special feature of the VELO is the ability to mechanically change the distance between the modules and the beams. In the closed state, the active pixels will be as close as 3.5 mm from the proton beams, allowing precise resolution of the reconstructed tracks and vertices during normal operation of the LHC [25]. On the other hand, this feature offers protection from unstable beam conditions by

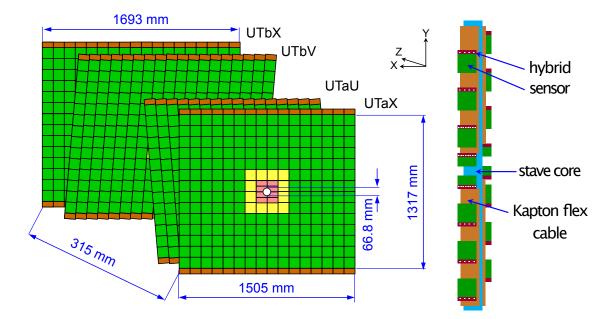

**Figure 2.4:** Schematic layout of the Upstream Tracker (UT) with the four detection layers (left). The detector is composed of four different sensor types: Type A (green), B (yellow), C and D (pink). It is built from vertical staves, which carry the sensors and readout hybrids as shown on the right. Image adapted from Ref. [27].

mechanically increasing the distance to the beams (open state). In order to allow for the two detector halves to be closed completely, the modules are slightly shifted along the beam axis relative to the opposing half. A schematic view of one VELO half as well as two opposing modules in the closed position are shown in Fig. 2.3.

### Upstream Tracker (UT)

The Upstream Tracker (UT) is located just in front, i.e. upstream of the dipole magnet. As shown in Fig. 2.4 (left), the detector is arranged in four detection layers that are equipped with silicon strip sensors. Each plane has an active area of approximately  $2 \text{ m}^2$ , which covers the full acceptance of the LHCb experiment. In order to obtain the highest possible hit resolution in the horizontal, bending direction of the magnet, the strips in the outer layers are oriented vertically. The resolution in the non-bending direction is achieved by rotating the two inner layers by  $\pm 5^{\circ}$ . Depending on the track occupancy and radiation dose, four different sensor types are in use. The majority of sensors (type A) have a strip pitch of 187.5 µm, while the pitch of the three sensor types closer to the beam pipe amounts to 93.5 µm [27].

The detector is built from a total of 68 elongated support structures that are referred to as staves. As illustrated in Fig. 2.4 (right), each stave is equipped with 14 to 16 silicon strip sensors. They are mounted from both sides with a slight overlap between neighbouring sensors. Each sensor is accompanied by a readout hybrid carrying up to eight custom front-end chips, called SALT. The radiation-hard chips

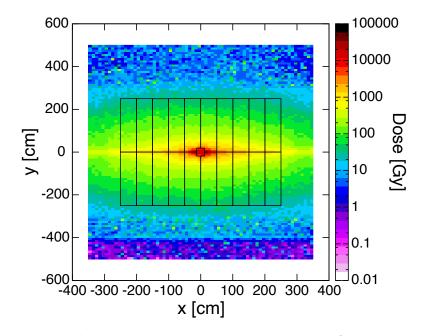

**Figure 2.5:** Expected dose in the *x-y* plane at z = 783 cm after an integrated luminosity of 50 fb<sup>-1</sup>. The Scintillating Fibre (SciFi) modules of the first tracking station located at this position are shown superimposed. The integrated dose absorbed in the fibres towards the centre peaks at about 35 kGy. Image modified from [20].

are based on 130 nm technology and were developed to sample the signals at the LHC frequency of 40 MHz. The resulting digital signals are sent via flex cables to the near-detector electronics [27].

#### Scintillating Fibre (SciFi) Tracker

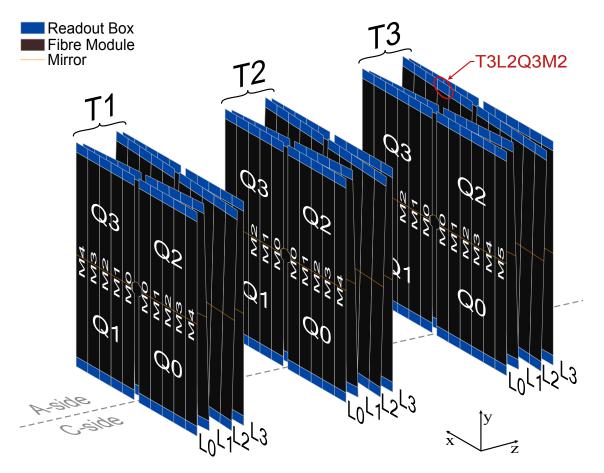

The last component within the LHCb tracking system is the Scintillating Fibre (SciFi) Tracker [20]. It consists of three stations that are located downstream of the magnet. Each station is composed of four detection layers that follow a similar geometry as the UT with the two inner layers being tilted by  $\pm 5^{\circ}$ . The active area, which amounts to about  $30 \text{ m}^2$  per layer, is built from staggered layers of scintillating fibres with a diameter of 250 µm. They are read out by arrays of silicon photomultipliers (SiPMs), which are located at the top and bottom of the detector outside of the geometrical acceptance. In the adjacent front-end electronics boxes, the SiPM signals are processed and digitised at the full LHC bunch crossing frequency of 40 MHz. The dimensions of one detector layer are illustrated in Fig. 2.5, along with the expected radiation dose at the position of the first station after an integrated luminosity of  $50 \text{ fb}^{-1}$ .

The SciFi Tracker and in particular its front-end electronics are the subject of this thesis and are therefore discussed in detail in the following chapters.

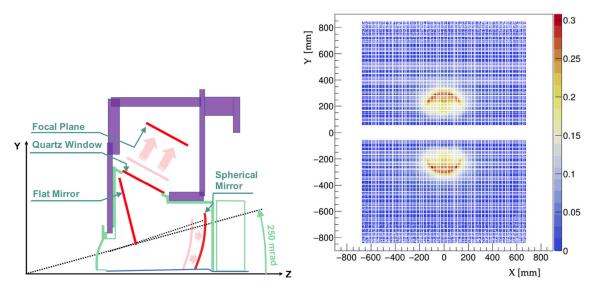

Figure 2.6: Schematic side view of the upper half of RICH1 (left) and simulated single channel occupancy (right). Modifications to the mechanical and optical system in the course of the upgrade are indicated by the red arrows in the side view. Images taken from Ref. [29].

## 2.3 Particle Identification

The particle identification (PID) capabilities play an important role for any flavourphysics experiment and has been essential for the success of LHCb during the first years of operation [28]. It consists of the Ring Imaging Cherenkov (RICH) system, two calorimeters and the muon stations. Compared to the tracking system, only small changes have been made to the PID system during the LHCb upgrade and mostly affect the RICH detectors.

#### Ring Imaging Cherenkov (RICH) Detectors

The main purpose of the RICH detectors is the separation of kaons and pions. This is achieved by utilising Cherenkov light, which occurs when a charged particle traverses a medium faster than the speed of light. In combination with the momentum as provided by the tracking system, the emission angle can be used to determine the mass of the particle.

Two separate detectors form the RICH system at LHCb and are referred to as RICH1 and RICH2. As shown in Fig. 2.1 on page 4, RICH1 is placed between the VELO and UT and covers the full angular acceptance of the detector and a momentum range of 10–50 GeV/c. On the other hand, RICH2 is located downstream of the SciFi Tracker and specialises in high momentum particles between 15–100 GeV/c with angles up to 120 mrad [29]. For these purposes, RICH1 uses  $C_4F_{10}$  gas as the medium, while  $CF_4$  is used in RICH2 [28].

While the enclosure of the RICH detectors could be reused in the upgrade, some

modifications to the mechanical and optical systems were required in order to expand the focal point and thereby reduce the channel occupancy. The modifications along with the simulated occupancy are shown in Fig. 2.6. Due to the performed changes, the maximum occupancy can be limited to 27% [29].

For both RICH1 and RICH2, commercial multi-anode photomultiplier tubes (MaPMTs) are used for the detection of the Cherenkov light, along with external frontend electronics. The 40 MHz readout is enabled by a custom designed, radiation-hard ASIC in 0.35 µm CMOS technology that is referred to as CLARO [30].

#### Calorimeters

The upgraded LHCb calorimetry system is composed of two sub-detectors that are located downstream of RICH2: an electromagnetic (ECAL) and a hadronic (HCAL) calorimeter [28]. Combined, they are responsible for the identification of electrons, photons and hadrons, as well as the determination of their energy. Both calorimeters employ a design with alternating layers of absorbers and scintillators. The produced scintillation light is transmitted via wavelength shifting fibres and is detected by photomultiplier tubes (PMTs).

One ECAL module is built from 66 stacked layers of lead absorbers (2 mm thick) and scintillators (4 mm). The module size varies from  $121.1 \times 121.1 \text{ mm}^2$  in the outer section of the ECAL, down to  $40.4 \times 40.4 \text{ mm}^2$  in the hottest region around the beam pipe. In contrast, the HCAL consists of alternating layers of scintillators (4 mm) and iron absorbers (16 mm), and employs two different module sizes of  $131.3 \times 131.3 \text{ mm}^2$  and  $262.6 \times 262.6 \text{ mm}^2$  in the inner and outer sections, respectively [19].

No changes to the calorimeter modules have been required during the upgrade since studies have shown that the granularity is sufficient even when being operated at a luminosity of  $2 \cdot 10^{33}$  cm<sup>-2</sup> s<sup>-1</sup> starting from LHC Run 3. However, new front-end electronics had to be developed to support the readout rate of 40 MHz, as well as having a higher preamplifier sensitivity in order to mitigate the gain degradation of the PMTs caused by increasing levels of radiation [25].

#### **Muon Stations**

Similar to the calorimeters and apart from redeveloping the front-end electronics for the trigger-less readout, the muon sub-detector remains mostly untouched during the LHCb upgrade. It consists of four stations downstream of the calorimeters which, for historical reasons, are designated as M2 to M5. They are equipped with multi-wire proportional chambers (MWPCs) in order to reconstruct the particle trajectories. By taking advantage of their penetrating power, a robust identification of muons is possible, which is achieved with the help of interleaved iron walls between the stations. The iron shielding is also the reason that no major changes are required in order to be operated at higher luminosities. One exception to this is the muon station M1 that was installed in front of the calorimeters in the initial LHCb experiment. Since it cannot withstand the huge hit occupancy expected at this location starting

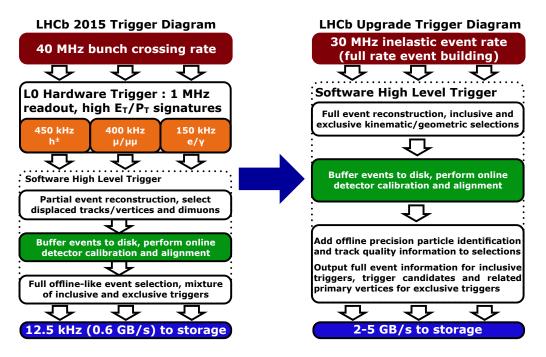

**Figure 2.7:** Trigger schemes for the initial (left) and upgraded LHCb experiment (right). Images taken from Ref. [31].

from LHC Run 3, it was removed in the course of the upgrade. The associated loss of information is marginal, as M1 was mainly used for the now redundant L0 trigger and was not part of the muon identification algorithms [28].

## 2.4 Trigger and Data Acquisition

Due to the high bunch crossing rate of 40 MHz at the LHC (30 MHz after excluding empty bunches), it is not feasible to store every event to disk for later access and analysis. In fact, during the first years of operation between 2010 and 2018, the readout of the front-end electronics of the complete detector was throttled to only a fraction of that rate. It was limited to 1 MHz as determined by the first trigger level (L0) implemented in hardware that had only access to the data provided by part of the detector [19].

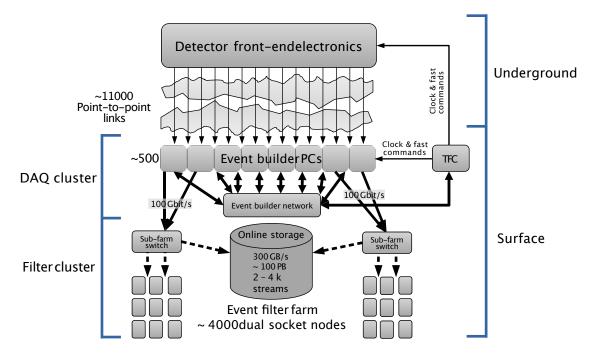

However, to take full advantage of the fivefold increase in luminosity starting from LHC Run 3, the trigger scheme had to be revised [32]. As illustrated in Fig. 2.7, the reconstruction of the complete event consisting of the data provided by all sub-detectors is now performed at the collision rate of 30 MHz. The full event reconstruction and selection is performed in a trigger level that is fully implemented in software, the so-called Software High Level Trigger. To allow for the 30 MHz readout, the front-end electronics of all sub-detectors had to be renewed as discussed previously. They are designed to be read out via simplex optical links using a common and custom protocol that is referred to as GBT [33]. A total of about

Figure 2.8: Layout of the DAQ system of the upgraded LHCb experiment. Image adapted from Ref. [36].

11 000 optical fibres, each carrying up to 4.48 Gbit/s of user data, transfer the data from the underground cavern to the server farm located on the surface of the LHCb site [34]. The so-called event builder servers are equipped with custom PCI Express readout cards and are responsible for the event reconstruction [35].

The reconstructed event information is used by a second cluster of servers referred to as event filter farm. They have access to a large disk-based buffer and run the selection algorithms in order to filter out the events to be kept for permanent storage [36]. The layout of the upgraded LHCb Data Acquisition (DAQ) system is shown in Fig. 2.8.

The detector front-end electronics and the readout cards are synchronised to the 40 MHz LHC clock by the Timing and Fast Control (TFC) system [37]. The distribution of the information is also done via optical links and the help of dedicated interface cards. An additional  $2 \times 2300$  bidirectional optical fibres are used for this purpose to enable the communication with the front-end electronics in the LHCb underground cavern [34]. By using the GBT protocol, the bandwidth along with the identical interface cards are shared for the implementation of the Experiment Control System (ECS). While the TFC distributes time-sensitive information to the different components within the DAQ system, the ECS is used for slow-control operations. These include for example the transmission of configuration parameters to the electronics, as well as reading out sensor values or error counters.

Further details about the readout and interface cards enabling the DAQ, TFC and ECS are given in Section 5.3.2.

# 3 The Scintillating Fibre Tracker

Up to the end of the LHC Run 2 in 2018, two different detector technologies have achieved an excellent tracking performance within the LHCb experiment [38]–[40]. The Scintillating Fibre (SciFi) Tracker is going to replace the tracking stations T1-T3 downstream of the magnet implementing a single technology based on scintillating fibres.

The layout and working principle of the detector is outlined in this chapter, along with the motivation that led to the upgrade of the tracking stations and its requirements. If not stated otherwise, the provided information is taken from the Technical Design Report (TDR) of the upgraded tracking system [20].

## 3.1 Motivation for the Tracker Upgrade

The Inner (IT) and Outer Tracker (OT), which have formed the downstream tracking stations of the initial LHCb experiment, were designed to provide a high precision estimation of the momentum of charged particles. This was achieved by operating at high hit efficiency as well as high resolution in the bending plane of the magnetic field.

The OT was a gaseous detector covering an area of approximately  $6 \text{ m} \times 5 \text{ m}$  per layer and consisted of 2.4 m long straw tubes with an inner diameter of 4.9 mm [41]. The tubes were filled with a mixture or argon, carbon dioxide and oxygen allowing for fast drift times below 50 ns. The detector modules were composed of two staggered layers of 64 straw tubes each and were arranged in three tracking stations (T1-T3). Each station consisted of four module layers following the so-called *x-u-v-x* geometry: Modules in the *x* layers were oriented vertically, while modules in the *u* and *v* layers were tilted by  $+5^{\circ}$  and  $-5^{\circ}$ , respectively. Consequently, a total of 24 straw tube layers were arranged along the direction of the beam pipe. The average hit efficiency was estimated to be 99.2 % and the position resolution was measured to be close to the design value of 200 µm [38]. Utilising novel real-time calibration methods as described in Ref. [39], the resolution could be further improved to 171 µm during LHC Run 2.

A plus-shaped area of approximately  $1.2 \text{ m} \times 0.4 \text{ m}$  in the centre of each layer was not covered by the OT and instead housed the IT. The IT was a silicon microstrip detector using 320 µm and 410 µm thick single-sided  $p^+$ -on-n sensors with a strip pitch of about 200 µm [42]. Individual silicon sensors were 7.8 cm in width and 11 cm in height and were contained within a total of 12 detector boxes. Each tracking station was composed of four boxes that were located above, below, and on both sides of the beam pipe, thus forming the aforementioned plus-shape. Each detector box was made up of four layers following the same x-u-v-x geometry as described above for the OT. Despite only covering about 1.3% of the geometrical acceptance, about 20% of all charged particles that were produced close to the interaction point were passing through the active area of the IT. The hit efficiency was estimated to be 99.7% and the resolution was measured to be 58 µm [40].

The initial tracking system was designed to limit the maximum occupancy in the OT to 10 % at nominal instantaneous luminosities  $\mathcal{L} = 2 \cdot 10^{32} \,\mathrm{cm}^{-2} \,\mathrm{s}^{-1}$ . It has been shown that it is possible to go beyond that design limit and efficiently find tracks at occupancies up to 25 % in the hottest regions of the OT [23]. The necessary improvements in the track reconstruction algorithms thereby allowed data collection at instantaneous luminosities  $\mathcal{L} = 4 \cdot 10^{32} \,\mathrm{cm}^{-2} \,\mathrm{s}^{-1}$ . However, going beyond  $\mathcal{L} = 10^{33} \,\mathrm{cm}^{-2} \,\mathrm{s}^{-1}$  has been found to require detectors of higher granularity. Different scenarios including an increased area of the IT along with shorter OT modules in the central part were considered. In the end, the decision towards a scintillating fibre tracker as a cost-effective, light and uniform detector covering the area of 30 m<sup>2</sup> per layer has been made.

## 3.2 Performance Requirements

The main objective of the tracking detectors within the LHCb experiment is the accurate determination of the momentum of charged particles. This information can be used to precisely measure the mass and lifetime of decayed particles. In order to achieve that, high hit efficiencies, as well as a good position resolution are necessary. In addition, the material budget has to be kept low to minimise multiple scattering, which is the main limiting factor for the momentum resolution of low momentum particles. Taking these considerations into account, the following requirements for the SciFi Tracker were formulated in the TDR [20]:

- Reaching high hit efficiencies at the level of 99%, while keeping the rate of reconstructed noise clusters low (< 10% of the recorded hits) at any location.</li>

- The single hit position resolution must be 100 µm or better in the bending plane of the magnet.

- Minimise the effect of multiple scattering by keeping the material budget low. Achieving radiation lengths  $X/X_0 < 1\%$  per detection layer is sufficient to not be the limiting factor compared to material upstream of the magnet.

- The readout electronics needs to operate and output data at the full LHC clock speed of 40 MHz. Inefficiencies due to dead time should be minimised by short recovery times.

- The aforementioned requirements should be met over the full lifetime of the upgraded LHCb detector up to an integrated luminosity of 50 fb<sup>-1</sup>.

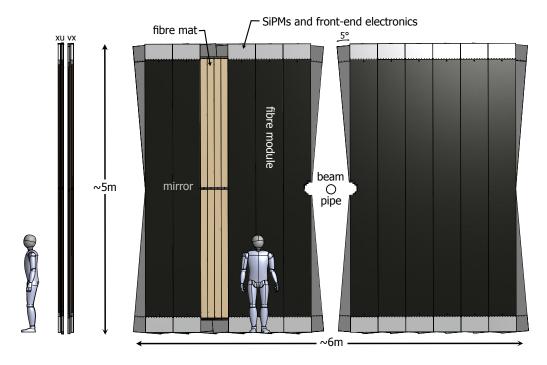

**Figure 3.1:** Schematic side (left) and front (right) view of the SciFi tracking station T3 with a 1.86 m tall human dummy for scale. Image adapted from Ref. [43].

## 3.3 Detector Design and Operating Principle

The SciFi Tracker fully replaces the OT and IT between the dipole magnet and RICH2 in the LHCb experiment. It is designed to follow the identical layout as its predecessors consisting of three stations T1-T3 with four detection layers each. The layers are arranged in the same x-u-v-x geometry with the two inner layers being tilted by  $+5^{\circ}$  and  $-5^{\circ}$  from the vertical axis. Each layer covers an area of approximately  $6 \text{ m} \times 5 \text{ m}$  and consists of a minimum of 10 fibre modules. The tracking station T3, which is furthest away from the interaction point, is equipped with two additional modules per layer to not limit the geometrical acceptance of the experiment. Figure 3.1 shows the schematic layout of the tracking station T3.

Each detector module is composed of a total of eight fibre mats that are read out by multichannel arrays of silicon photomultipliers (SiPMs) located at the top and bottom of the detector. The fibre mats itself consist of six staggered scintillating fibre layers with 250 µm in diameter.

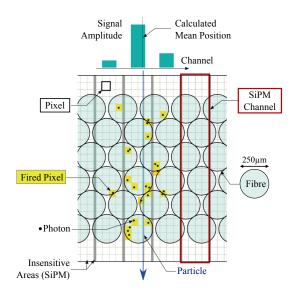

The operating principle is illustrated in Fig. 3.2. Charged particles that traverse the layers of scintillating fibres dissipate energy as ionisation and excitation. Subsequently, the absorbed energy is transformed into luminescence emission in the scintillation medium [44]. Photons that are emitted along the fibres are trapped inside by total reflections at the fibre boundaries. They follow the course of the fibres until they reach the SiPM channels at the fibre ends.

The amplitude of the resulting electrical signal is proportional to the number of

Figure 3.2: Operating principle of the LHCb Scintillating Fibre Tracker. Image adapted from Ref. [20].

**Figure 3.3:** Longitudinal (top) and cross (bottom) section of a multicladding scintillating fibre with exemplary trajectories of trapped photons. Image taken from Ref. [45].

pixels that are hit by photons within each channel. The average light yield, i.e. the number of pixels hit, per traversing particle is in the order of 20 depending on the incident angle and distance from the SiPM array. However, irradiating the fibres with expected doses after  $50 \, \text{fb}^{-1}$  results in a loss of light yield by about  $40 \,\%$ . The position of the corresponding hit can be defined as the location of involved SiPM channels weighted by their signal amplitudes.

## 3.4 Scintillating Fibres

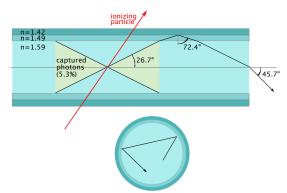

The SciFi Tracker employs scintillating fibres with a round cross section of 250 µm in diameter produced by Kuraray<sup>1</sup>. Fibres of type SCSF-78MJ were chosen for achieving a fast decay time of 2.4 ns and a large attenuation length of about 3.5 m [46]. A high light yield is achieved by utilising a multi-cladding structure with descending refractive indices towards the surface of the fibre, while also being mechanically more robust. The inner cladding is made of Polymethylmethacrylate (PMMA, n = 1.49) and surrounds the Polystyrene (PS, n = 1.59) core, while Fluorinated polymer (FP, n = 1.42) is used as the outer cladding. Each cladding is about 4 µm in thickness [47]. Following Snell's law about the angle dependence of light passing the boundary

<sup>&</sup>lt;sup>1</sup>Kuraray Co., Ltd., Tokyo, Japan

of two isotropic media, there exists a critical angle of incidence

$$\theta_{\rm crit} = \arcsin\frac{n_2}{n_1} \tag{3.1}$$

above which total internal reflection at the boundary occurs. For the transition between the inner ( $n_1 = 1.49$ ) and outer cladding ( $n_2 = 1.42$ ) the critical angle can be calculated as  $\theta_{\text{crit, PMMA}\to\text{FP}} = 72.4^{\circ}$ . This translates to a maximum opening angle of  $2 \times 26.7^{\circ}$  at the centre of the fibre as illustrated in Fig. 3.3. Assuming an isotropic photon emission, the trapping efficiency is thereby given as 5.3%. Following similar considerations, having a single-cladding fibre with a PS core and PMMA cladding only results in a 3.1% trapping efficiency.

Pure Polystyrene has a relatively poor quantum efficiency and long relaxation time. Therefore, a small amount (about 1% in weight) of p-Terphenyl is added to the PS core. This organic fluorescent dye rapidly (below 1 ns) absorbs the excitation energy of the PS base via a non-radiative dipole-dipole interaction known as Förster Transfer [48]. Subsequently, the absorbed energy is released by the emission of a photon. The fluorescent dye has been chosen for its high quantum efficiency > 95% and fast decay times below a few ns [20].

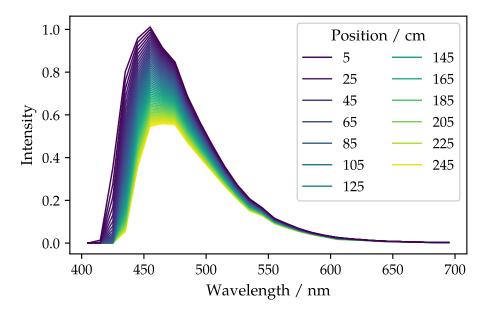

A secondary dye is added to the PS core in a very low concentration (below 1 ‰ in weight). It acts as a wavelength shifter by absorbing the emission of the primary dye and re-emitting photons at a longer wavelength at which re-absorption in the fibre occurs less frequently [49]. Tetraphenyl butadiene (TPB) is used as the secondary dye in the scintillating fibres of type SCSF-78MJ and enables the required large attenuation length. Figure 3.4 shows the resulting photon emission spectrum of the scintillating fibres, which peaks between 450 nm and 500 nm depending on the distance to the point of excitation.

More than 10000 km of fibres are used for the SciFi Tracker and were delivered to CERN in 48 individual shipments between 2016 and 2018. Every batch of fibres was subject to a detailed test procedure [46]: Samples were taken to evaluate the attenuation length before and after being exposed to X-ray irradiation in order to reveal impurities in the used materials. The ionisation light yield was measured using energy filtered 1 MeV electrons from a Sr-90 radioactive source. In addition to that, for every km of fibre, the quality of the cladding and uniformity of the diameter was verified. Fibre bumps up to 500 µm in diameter were detected and removed by a hot shrinking procedure in a fully automatic manner [51], while larger bumps were cut out manually. The conducted quality assurance measures ensured that only high quality fibres were assembled into the fibre modules as described in the following.

## 3.5 Fibre Modules

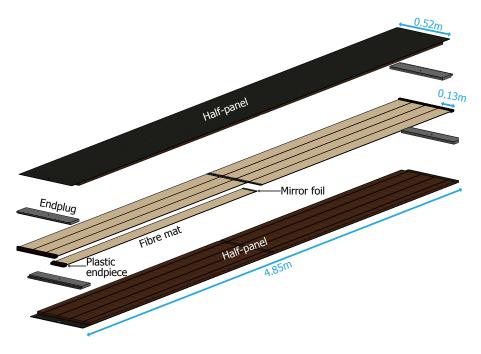

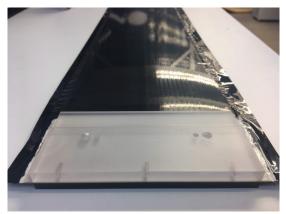

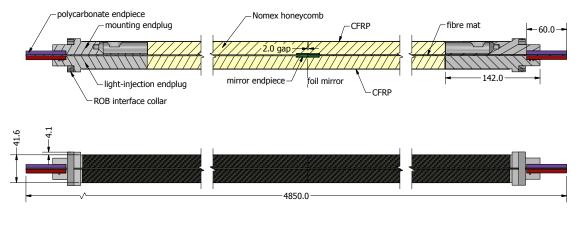

The fibre modules constitute the active part of the SciFi Tracker. In total, 128 of these modules are used and are arranged in 12 layers and 3 stations as described in Section 3.3. Each fibre module is 4.85 m long and 0.52 m in width. Figure 3.5 shows

Figure 3.4: Emission spectrum of a scintillating fibre of type SCSF-78MJ at different distances to the point of excitation. For short distances, the maximum is located at around 450 nm and shifts towards larger wavelengths with increasing distance due to self-absorption of the inserted wavelength shifter. Image taken from Ref. [50].

an exploded view of one fibre module with its key constituents. The core of one module consists of eight fibre mats that are arranged in two rows with four mats lying side by side in each row.

The width of each fibre mat is about 0.13 m and was chosen as a compromise between covering a large area and still being easy to handle. Following similar considerations, the length was chosen such that two mats are required to cover the full module length of 4.85 m. Even though this design introduces a small gap of about 2 mm at the centre of the module between the two rows of fibre mats, it bears the additional advantage that the light yield of a single particle crossing is concentrated into fewer SiPM channels on only one side of the module. Photons that are emitted towards the centre of the module are reflected back to the outside by a mirror foil that is glued to the fibre mat end.

The fibre mats are sandwiched between two half-panels that are made of a carbon fibre, honeycomb structure. The half-panels provide the necessary mechanical stiffness to the modules while keeping the material budget low.

#### Fibre Mats

The main components of the modules are the fibre mats. Each fibre mat consists of six layers of scintillating fibres as described in Section 3.4 and measures about 2.4 m in length and 0.13 m in width. Figure 3.6 shows the cross section of one fibre mat.

A fibre pitch of  $275 \,\mu\text{m}$  is chosen to be  $10 \,\%$  larger than the nominal fibre diameter to allow for small production tolerances. Proper fibre positioning is achieved by

Figure 3.5: Exploded view of one fibre module of the SciFi Tracker. Image adapted from Ref. [52].

Figure 3.6: Cross section of one fibre mat used in the SciFi Tracker. Image taken from Ref. [50].

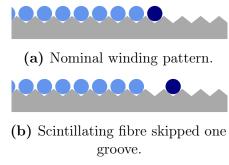

winding the fibre mats on a threaded wheel with a diameter of about 0.82 m [52]. While the scintillating fibres in the first layer are guided by the grooves in the winding wheel, fibres in subsequent layers fall into the gaps of the underlying layer. This results in the staggered arrangement of the layers as can be seen in Fig. 3.6.

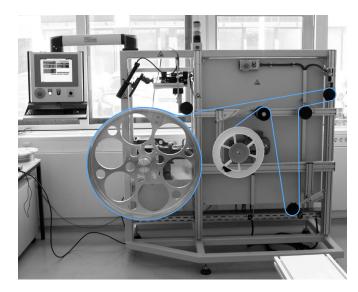

Epoxy glue loaded with  $\text{TiO}_2$  is added during the winding process to bond the fibres together, while also providing a thin protection coating on the surface. Additionally, the glue gets filled into 2 mm deep holes that are located in the winding wheel with a distance of about 245 mm to each other around the circumference of the wheel. After curing, the glue sticks to the fibre mat resulting in small pins that are used to align the mats with a precision of better than 100 µm in the x-direction during the module production [20]. A close-up view of one alignment pin is shown in Fig. 3.9 on page 21. The machine used for the serial production of the fibre mats is shown in Fig. 3.7.

A reliable winding of the fibre is enabled by applying a constant tension using a

Figure 3.7: Winding machine for the serial production of the fibre mats for the SciFi Tracker. The path of the wound fibre is highlighted in blue. Image taken from Ref. [52].

(c) Scintillating fibre jumped to a higher layer.

Figure 3.8: Nominal pattern (a) and different types of errors (b,c) that can occur during the winding of a fibre mat. Images adapted from Ref. [52].

dancer roller system. However, different types of errors can occur during the winding of the fibre mats and are illustrated in Fig. 3.8. The winding procedure is monitored with a monochromatic industrial camera that feeds its output to a Convolutional Neural Network (CNN) [53]. This approach allows for a semi-automatic winding procedure where manual intervention is only needed in case of detected defects [50].

After the actual winding is performed, a  $25 \,\mu\text{m}$  Kapton foil is applied to the accessible side of the fibre mat. The foil acts as an additional protection layer while also shielding the scintillating fibres from external light sources. Afterwards, the fibre mat is cut at a predefined location on the winding wheel perpendicular to the fibre direction and taken off the wheel. In the process, the fibre mat immediately shrinks in the order of 1 cm due to the constant tension applied during the winding. The removed mat is heated up to  $40 \,^\circ\text{C}$  to flatten it. Afterwards, the Kapton foil is applied from the remaining side, leaving out small cutouts for the alignment pins.

At this stage, the fibre mat is still slightly larger than the final dimensions. The nominal length of 2424 mm [52] is defined by so-called end pieces made from plastic that are glued to both sides on both ends of the fibre mat. The excess parts of the mat are pre-cut using a saw blade and further processed using a diamond milling head. On one side of the mat, the SiPM arrays will be pressed against the smooth surface that is obtained in this way. On the other side, a mirror foil is applied to reflect back photons that are emitted away from the SiPMs in order to increase the overall light yield. An aluminized Mylar foil is used for that purpose which proved to reach a reflectivity in the order of 80% [54].

All the steps listed previously were performed in four different locations: TU

Figure 3.9: Close-up view on a wound fibre mat with alignment pin. Image taken from Ref. [50].

Figure 3.10: Finished and laminated fibre mat with plastic end piece. Image taken from Ref. [50].

Dortmund, RWTH Aachen, EPFL in Lausanne and Kurchatov Institute in Moscow. A total of 1024 fibre mats that are needed for the complete detector plus spares were produced in these winding centres. A finished fibre mat is shown in Fig. 3.10 and is already cut to its nominal length. However, when leaving the winding centres, the width is still slightly larger than their nominal value and they feature excess Kapton foil to both edges. This allows for a safe transport to the module assembly centres, where the mats are embedded into the mechanical support structure of the fibre modules.

### **Mechanical Support Structure**

The wound fibre mats that are produced in the winding centres are shipped to two different locations in order to get assembled to full-size detector modules. In these so-called module assembly centres, which are at Heidelberg University and Nikhef in Amsterdam, the fibre mats are embedded into a support structure that provides mechanical stiffness and protection to the modules. Before that can happen, the excess Kapton foil needs to be removed and the fibre mats need to be cut to their nominal width of 130.65 mm.

Afterwards, eight fibre mats are laid out in the final  $2 \times 4$  arrangement as shown in Fig. 3.5 on page 19 onto a high precision template made from a single aluminium plate. The alignment pins of the mats are facing down and are guided by four longitudinal grooves in the template. The grooves have a centre-to-centre distance of 130.8 mm leaving a gap of 0.15–0.20 mm in-between two neighbouring fibre mats to account for tolerances of the longitudinal cut. The positioning follows the geometry of the SiPM arrays (see Section 3.6) such that no additional loss of acceptance is introduced by the gaps.

In the next step, glue is applied on the surface of the fibre mats that bonds the mats to the 2 cm thick support structure made from a light core material (Nomex

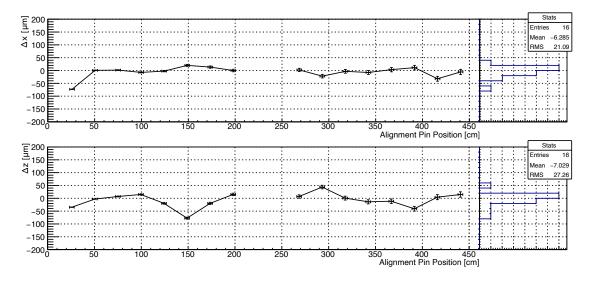

Figure 3.11: Evaluation of the straightness of two facing fibre mats within a fibre module using a test setup consisting of a laser and a beam camera. The deviations from a straight line along the alignment pins are shown in both the x (top) and z (bottom plot) direction within the LHCb coordinate system.

honeycomb). At the ends of the modules, the honeycomb is cut out to provide space for four individual pieces of aluminium, the so-called end plugs. The end plugs act as an anchor point to mount and align the fibre modules in the detector. Additionally, they house the light injection system (see Section 4.5) that is used for calibrating the individual channels. The outer shell of a fibre module consists of a carbon fibre reinforced polymer (CFRP) skin that is 200 µm thick and provides the necessary stiffness to the module.

The partially assembled module is turned over to the other side and placed onto another, flat aluminium template. In this position, the placement and straightness of the fibre mats within the module is verified using a test setup consisting of a laser and a beam camera: The laser is positioned on one side of the module pointing along the centre of two facing fibre mats. The beam camera is successively positioned on top of the total of 16 alignment pins on the two mats and the position of the beam projection is recorded. The camera is mounted on an aluminium block with the same kind of groove as in the aluminium template to allow for an accurate placement on top of the alignment pins. Like this, the straightness of the fibre mats in the module can be evaluated by the deviation of the recorded beam projections to a straight line in both the horizontal and vertical direction with respect to the setup on the assembly table, corresponding to the x and z direction within the LHCb coordinate system. Figure 3.11 shows the exemplary result of two facing fibre mats demonstrating a straightness of better than the required 100 µm along all pins.

After the straightness of the fibre mats is verified, the module is closed from the remaining side using another half-panel consisting of honeycomb core material and a CFRP skin. In order to provide light-tightness to the module, it is finished by

#### **Cross Section**

Figure 3.12: Cross section and side view of a fibre module of the SciFi Tracker. The dimensions shown in this image are given in mm. Image taken from Ref. [52].

closing the sides with CFRP sidewalls. Figure 3.12 shows the schematic side view and cross section of a finished fibre module. At this stage, the scintillating fibres are only exposed to the outside between the plastic end pieces of the fibre mats on both sides of the module. They will later be covered by the SiPM arrays (see Section 3.6).

Special modules need to be produced to account for the beam pipe as indicated in Fig. 3.1 on page 15. They feature a rectangular  $13 \text{ cm} \times 11.5 \text{ cm}$  cutout on one side of the module. To allow for this, the two fibre mats on this side of the module are produced with a reduced length. The originally intended circular cutout was found to be difficult to realise due to the mirror foil that needs to be applied to the fibre mat ends [55].

The material budget of the individual components of a SciFi Tracker module are listed in Table 3.1. The aluminium end plugs are not considered because they lie outside the acceptance of the experiment. The total radiation length for one module is  $0.984 \% X_0$  which translates to  $3.936 \% X_0$  for one tracking station consisting of four detection layers. This value fulfills the required limit on the material budget as listed in Section 3.2. While the Nomex honeycomb structure accounts for 95% of the module's thickness, it only contributes about 31% to the total radiation length. Note that the total thickness given in Table 3.1 is slightly larger than the nominal value of 41.6 mm due to submersion of the glue into the honeycomb [52].

In total, 128 fibre modules needed for the detector plus spares were produced at the two module assembly centres between 2016 and 2019. Of these, about 20% are special modules with a rectangular cutout on one side to account for the beam pipe in the centre of each of the 12 detection layers.

| Material             | Thickness $\Delta z$ [µm] | Radiation length $X_0$ [cm] | $\Delta z/X_0$ [%] |

|----------------------|---------------------------|-----------------------------|--------------------|

| Scintillating fibres | 1350                      | 33.2                        | 0.407              |

| Kapton foil          | $2 \times 25$             | 28.6                        | 0.017              |

| Panel assembly glue  | $4 \times 75$             | 36.1                        | 0.083              |

| Nomex honeycomb      | $2 \times 20000$          | 1310.0                      | 0.305              |

| Carbon fibre skin    | $2 \times 200$            | 23.3                        | 0.172              |

| Total                | 42100                     |                             | 0.984              |

**Table 3.1:** Material budget for a scintillating fibre module. Data taken from [52], [56].

# 3.6 Silicon Photomultipliers

Silicon photomultipliers (SiPMs) are solid state devices that allow for the detection of individual photons. Combined with their small dimensions and high granularity they meet the needs for a high resolution tracker like the SciFi [20].

## **Operating Principle**

The functionality of solid state photon detectors is based on a p-n junction, which refers to the boundary between n- and p-doped regions inside a semiconductor material. Close to the boundary, electrons from the n-doped region diffuse into the p-doped region and, vice versa, electron holes from the p-doped region diffuse into the n-doped region. By recombination of electrons and holes in the area around the boundary, the so-called depletion zone, the amount of free charge carriers is reduced significantly resulting in a low electrical conductivity. The diffusion continues until the electrical potential that is generated in the process counteracts the motion of the charge carriers.

**Forward Bias** By applying a positive external voltage to the *p*-side with respect to the *n*-side (forward bias) the diffusion process is reversed. When the bias voltage is large enough, the depletion zone becomes very thin and the *p*-*n* junction becomes conductive allowing for a (forward) current flow.

**Reverse Bias** Applying a negative external voltage to the *p*-side with respect to the *n*-side (reverse bias) has the opposite effect: The depletion zone expands and the electrical conductivity stays low. Only a small (reverse) current can flow.

A photodiode makes use of operating a p-n junction with a reverse bias voltage applied. Photons with sufficient energy can create electron-hole pairs in the depletion zone via the photoelectric effect. A free electron that is generated by this process is

called (primary) photoelectron (pe). Since the resulting current flow only consists of individual charge carriers, photodiodes are not suitable for low intensity applications like the SciFi Tracker.

Avalanche photodiodes (APD) overcome this issue by operating at higher voltages. The thereby increased electrical field at the p-n junction accelerates the primary photoelectrons up to energies at which they can create electron-hole pairs themselves. This process can repeat itself several times causing an avalanche of charge carriers that is measurable as an electrical current.

When the applied voltage is increased even further, beyond the breakdown voltage  $V_{\rm BD}$ , a single primary photoelectron can cause a self sustaining avalanche (Geiger mode). The released charge is independent of the number of primary photoelectrons and results in a permanent current if unquenched. In practice, the avalanche is typically interrupted by inserting a resistor in series to the photodiode. As the current flow increases during the emerging avalanche, the applied voltage is lowered below the breakdown voltage by the so-called quench resistor  $R_{\rm Q}$  such that no more charge carriers can be created.

SiPMs are composed of an array of APD pixels that are operated in Geiger mode (G-APD). They are connected in parallel such that the resulting signal is proportional to the number of pixels with a triggered avalanche. If the probability for multiple photons hitting the same pixel is low, SiPMs allow for the counting of individual photons. This is given when the number of pixels is much greater than the number of incident photons. The amplitude of a signal is typically stated in units of generated primary photoelectrons (X pe), which is equivalent to the number of involved pixels in low light conditions.

#### Correlated and uncorrelated Noise

SiPMs are subject to different types of noise that affect the operation. One distinguishes between correlated and uncorrelated noise.

**Correlated Noise** The emergence of correlated noise is, as the name suggests, correlated to the occurrence of an initial signal. A large contribution comes from crosstalk. Crosstalk originates from infrared photons that are emitted in a pixel during an avalanche. These photons can reach neighbouring pixels causing another discharge. Depending on the region where the photon is absorbed, the resulting pulse either happens instantaneously (**direct crosstalk**, within a few 100 ps) or with a significant delay up to 100 ns (**delayed crosstalk**) with respect to the initial signal [57].

Delayed crosstalk must not be confused with **afterpulses**, which have a different formation mechanism. Afterpulses occur due to defects in the silicon lattice that can act as charge traps. A charge carrier created during an avalanche can get caught in these traps. When it is released at a later time, it can trigger another discharge in the same pixel causing a second, delayed pulse distributed over a few 100 ns [57].

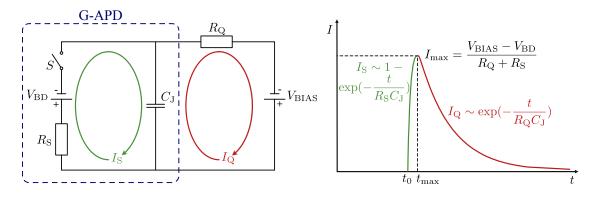

Figure 3.13: Electrical circuit of a basic equivalent model for an externally biased G-APD (left). The plot on the right shows the signal pulse after closing (at  $t_0$ ) and re-opening (at  $t_{\text{max}}$ ) the switch S. Image inspired from Ref. [58].

**Uncorrelated Noise** Instead of being excited by an incident photon, an electronhole pair in the depletion zone can also be generated by thermal excitation. The resulting signal is indistinguishable from a photon induced avalanche. This type of noise can occur randomly and is independent of any initial signal. Because of that, it is also referred to as **dark counts**. Due to the thermal origin, the dark count rate (DCR) strongly depends on temperature. In addition to that, the DCR increases after irradiation.

Various combinations of the different types of noise can occur. For example, it is not uncommon that a dark count arises in conjunction with a crosstalk event. The amplitude of the resulting signal is thereby increased making it more difficult to be identified as noise.

#### **Basic electrical Model**

Following Ref. [58], a basic electrical model of a G-APD can be developed to derive the key characteristics of the signal pulse. It consists of the breakdown voltage  $V_{\rm BD}$ , capacity  $C_{\rm J}$  and ohmic resistance  $R_{\rm S}$  of the G-APD, as well as the quench resistor  $R_{\rm Q}$  and bias voltage  $V_{\rm BIAS}$ . A conceptual switch S is responsible for initiating (S is closed) and terminating (S is open) the avalanche.

Figure 3.13 (left) shows the electrical circuit of the model. In the absence of incident photons and ignoring dark noise, the switch S is open. The capacitor  $C_{\rm J}$  is fully charged by the applied bias voltage  $V_{\rm BIAS}$ . No current is flowing. Then, representative for an incident photon triggering an avalanche, the switch S is closed at time  $t_0$ . The capacitor  $C_{\rm J}$  begins discharging through the series resistor  $R_{\rm S}$  as a flowing current

$$I_{\rm S}(t) \sim 1 - \exp\left(-\frac{t}{R_{\rm S}C_{\rm J}}\right) \equiv 1 - \exp\left(-\frac{t}{\tau_{\rm S}}\right)$$

(3.2)

with a time constant  $\tau_{\rm S}$ . At  $t_{\rm max}$ , which is in the order of 1 ns after  $t_0$  [58], the maximum current

$$I_{\rm max} = \frac{V_{\rm BIAS} - V_{\rm BD}}{R_{\rm Q} + R_{\rm S}} \equiv \frac{\Delta V}{R_{\rm Q} + R_{\rm S}}$$

(3.3)

is reached. The introduced variable  $\Delta V$  is called overvoltage. At this time, the applied voltage to the G-APD drops down to approximately  $V_{\rm BD}$ , which is not sufficient to sustain the avalanche. The switch S opens and the capacitor  $C_{\rm J}$  is recharged by a current

$$I_{\rm Q}(t) \sim \exp\left(-\frac{t}{R_{\rm Q}C_{\rm J}}\right) \equiv \exp\left(-\frac{t}{\tau_{\rm Q}}\right)$$

(3.4)

with a time constant  $\tau_{\rm Q}$ , which is also referred to as the recovery time. The shape of the resulting signal is shown in Fig. 3.13 (right). For  $R_{\rm Q} \gg R_{\rm S}$  and thereby  $\tau_{\rm Q} \gg \tau_{\rm S}$ , the total charge Q, i.e. area under the signal shape, can be derived as

$$Q = I_{\max} \cdot \tau_{\rm Q} = \frac{\Delta V}{R_{\rm Q} + R_{\rm S}} \cdot R_{\rm Q} C_{\rm J} = \Delta V \cdot C_{\rm J} \,. \tag{3.5}$$

Since the avalanche is triggered by a single primary electron with elementary charge e, the charge amplification factor – or gain G – is given by

$$G = \frac{Q}{e} = \frac{\Delta V \cdot C_{\rm J}}{e} \,. \tag{3.6}$$

Typical operation values for the gain of SiPMs lie between  $10^5$  and  $10^7$  [58].

#### Application at the SciFi Tracker

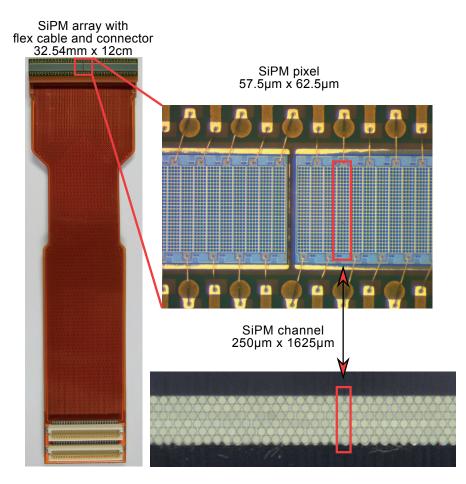

The SciFi Tracker utilises a total of 524 288 SiPM channels that are grouped in 128-channel arrays. The multichannel arrays referred to as H2017 are custom-made and produced by Hamamatsu<sup>1</sup>. One array is 32.54 mm wide and consists of two dies with 64 channels each. The silicon dies are protected with a thin 105 µm epoxy layer [59]. After mounting in the detector, the insensitive area between two adjacent SiPM arrays amounts to 480 µm, while the specifications state the gap between the two dies to be  $(220 \pm 50)$  µm [60]. The geometry was chosen such that the width of multiple arrays match the fibre mat and module dimensions. One mat is instrumented with four SiPM arrays, which translates to 16 arrays for a fibre module on each end. Figure 3.14 shows a photo of a H2017 package with a zoomed in view on the individual SiPM channels. The package is mounted on a Kapton flex PCB (Printed Circuit Board) that is about 12 cm long. Two 80-pins, 0.5 mm pitch connectors<sup>2</sup> are placed on the other end of the flex PCB to provide the SiPM

<sup>&</sup>lt;sup>1</sup>Hamamatsu Photonics K.K., 325-6, Sunayama-cho, Naka-ku, Hamamatsu City, Shizuoka Pref., 430-8587, Japan

$<sup>^2\</sup>mathrm{DF12}(3.0)\text{-}80\mathrm{DP}\text{-}0.5\mathrm{V}$  by Hirose Electric Co., Ltd.

Figure 3.14: Hamamatsu H2017 128-channel SiPM array with flex cable and connector as used for the SciFi Tracker (left). A zoomed in view on the active area with the gap between the two dies is shown on the right, as well as an illustration of the position of one SiPM channel with respect to the fibre mat. Image adapted from Ref. [59].

connections to the front-end electronics (see Section 3.7).

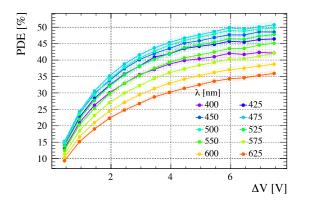

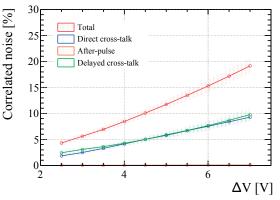

The SiPM channel pitch is 250 µm thus matching the diameter of the scintillating fibres. The height is with 1625 µm about 20 % larger than the fibre mat to allow for slight misalignments during the assembly. One channel is composed of  $4 \times 26$ pixels each covering an area of 57.5 µm × 62.5 µm. As shown in Fig. 3.15, the large pixel size allows for high photon detection efficiencies up to 44 % at the nominal overvoltage  $\Delta V = 3.5$  V [57] for the relevant wavelengths from 400 nm to 600 nm (compare with Fig. 3.4 on page 18). Additionally, it enables the application of isolating trenches to suppress crosstalk. Figure 3.16 shows the crosstalk probability for different overvoltages  $\Delta V$ , as well as the probabilities for other types of correlated noise. At the nominal overvoltage  $\Delta V = 3.5$  V, the total probability for correlated noise amounts to about 7%. It is split equally between the two types of crosstalk: direct and delayed. Afterpulses practically do not play a role for H2017 arrays.

Figure 3.15: Measured photon detection efficiencies (PDE) based on a pulse counting approach for an H2017 SiPM array for different wavelengths  $\lambda$  and overvoltages  $\Delta V$ . Image taken from Ref. [57].

Figure 3.16: Probabilities for different types of correlated noise as determined during the quality assurance of 5000 H2017 SiPMs. Variations in the order of  $\pm 1\%$  were observed between the different devices. Image taken from Ref. [61].

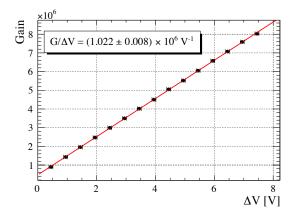

The typical gain for an H2017 SiPM array is  $G = 4 \cdot 10^6$  at the nominal overvoltage. Figure 3.17 shows the dependence of the gain on the overvoltage for one channel. As derived in Eq. (3.6) on page 27, it follows a linear relation. The recovery time is found to be  $\tau_{\rm Q} = (84.6 \pm 0.2)$  ns. The breakdown voltage  $V_{\rm BD}$  ranges from 51.0 V to 52.5 V as determined among 20 devices from the production batch. Within one array, it typically varies by  $\pm 300 \,\mathrm{mV}$  [59]. When operated at the same voltage around the nominal overvoltage  $\Delta V = 3.5 \,\mathrm{V}$ , this results in a gain uniformity of better than 10% as required in the TDR [20].

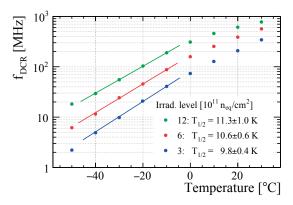

A key parameter for the operation of the SciFi Tracker is the rate at which dark counts occur (DCR), as it is main source of noise for the detector. As described previously, the DCR strongly depends on both temperature and irradiation dose, specifically the 1 MeV neutron-equivalent fluence ( $n_{eq}/cm^2$ ). Towards the end of the lifetime of the upgraded detector, the expected fluence that the SiPMs will have received is  $6 \cdot 10^{11} n_{eq}/cm^2$  [20]. At that time, the DCR will reach values of several hundred MHz at room temperature, while the DCR of an unirradiated SiPM is in the order of kHz. This drastic increase resulting from lattice deformations is mitigated by cooling of the SiPM arrays. As shown in Fig. 3.18, the DCR can be reduced by 50 % with every decrease in temperature by about 10 °C. Thereby, at the end of LHC Run 4, manageable DCRs in the order of 10 MHz can be reached at -40 °C. Reaching low DCRs of irradiated SiPMs at -40 °C was a main criteria for the selection of the best suited technology during the R&D phase of the SciFi Tracker.

The temperature of each array can be monitored with the help of a Pt1000 temperature sensor<sup>1</sup> that is mounted on the backside of the SiPM array. The specific

<sup>&</sup>lt;sup>1</sup>Pt1000 SMD 0603 Class B by Heraeus Nexensos GmbH

Figure 3.17: Dependence of the gain on the overvoltage for one H2017 SiPM channel. The red line shows the result of a linear fit to the data. Image taken from Ref. [57].

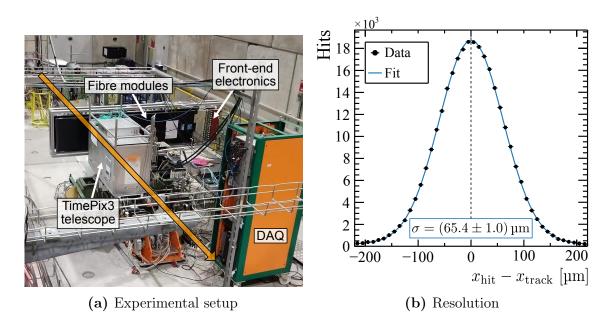

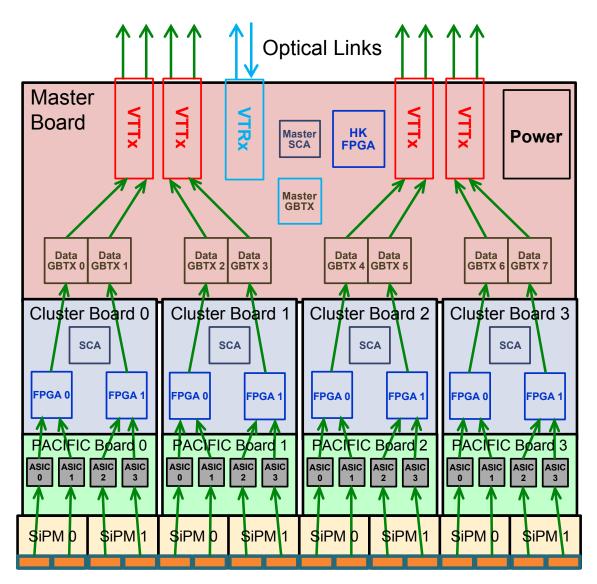

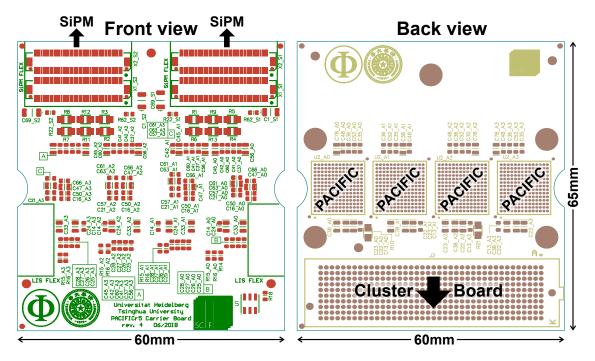

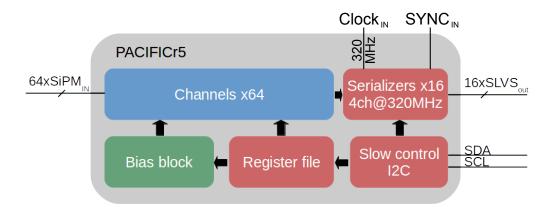

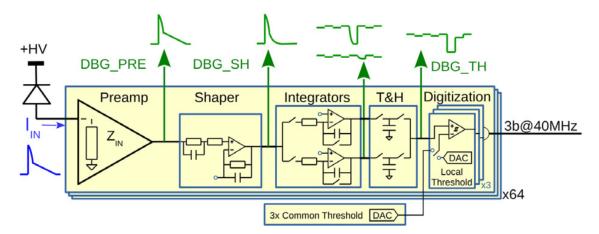

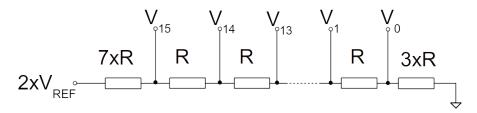

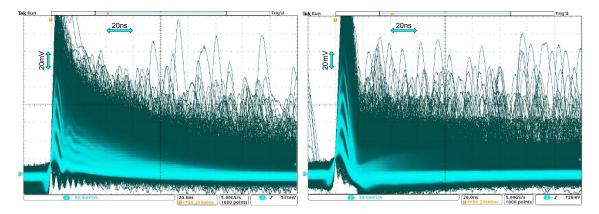

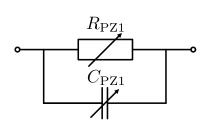

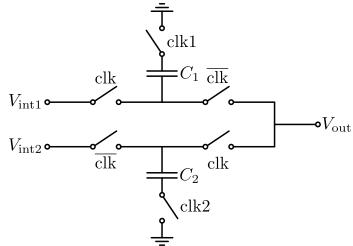

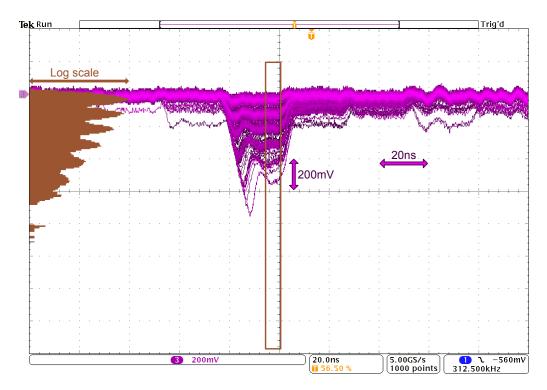

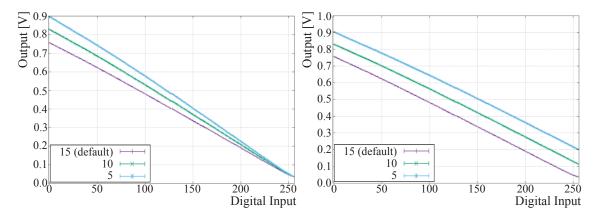

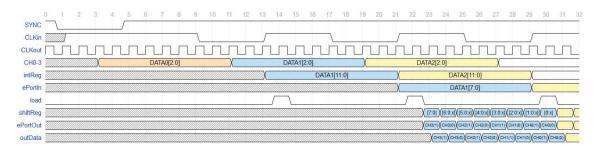

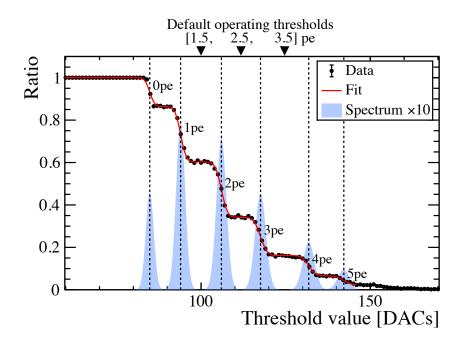

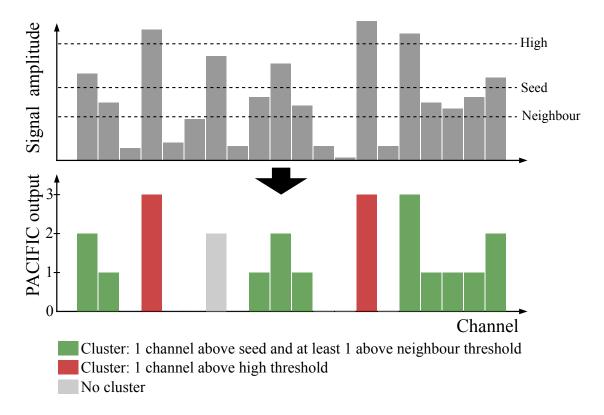

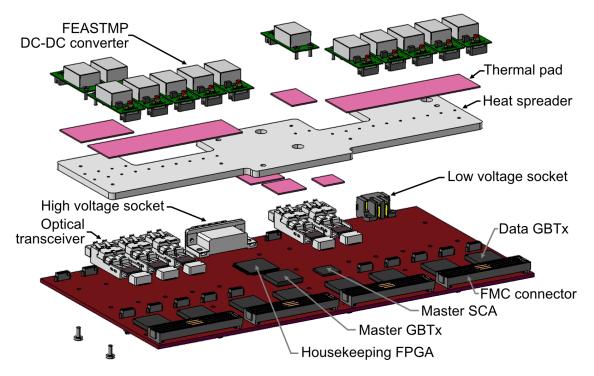

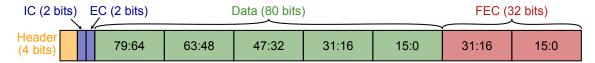

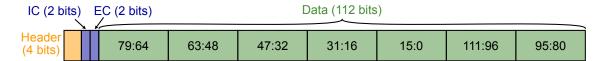

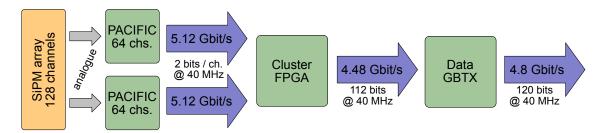

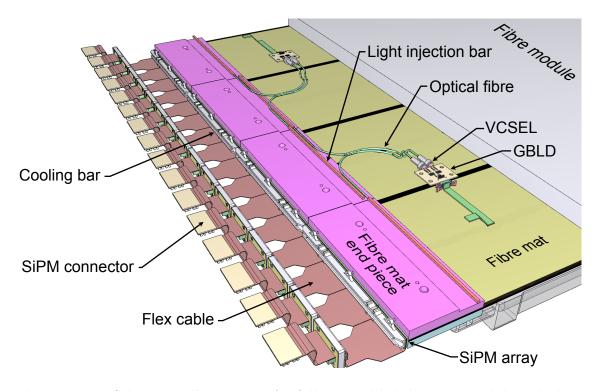

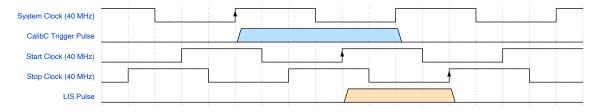

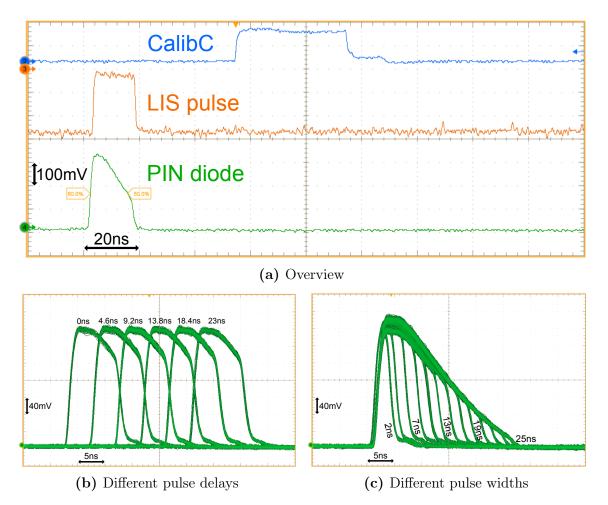

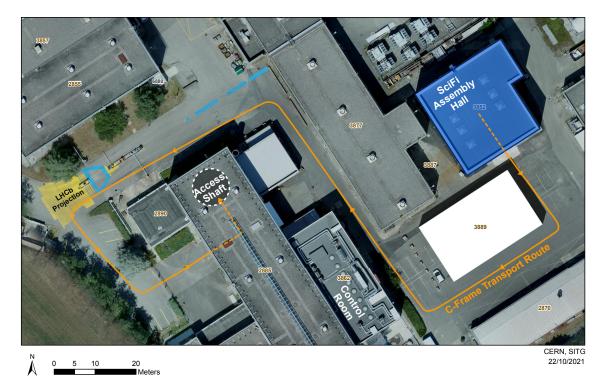

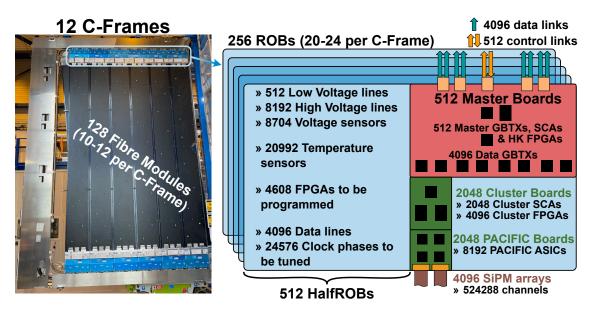

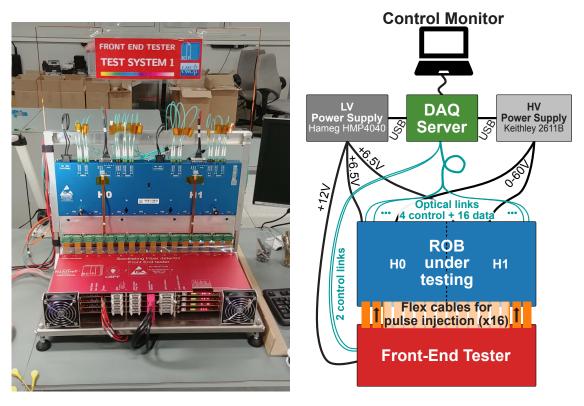

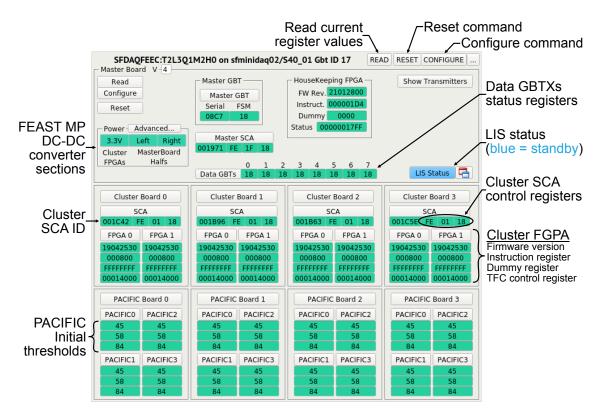

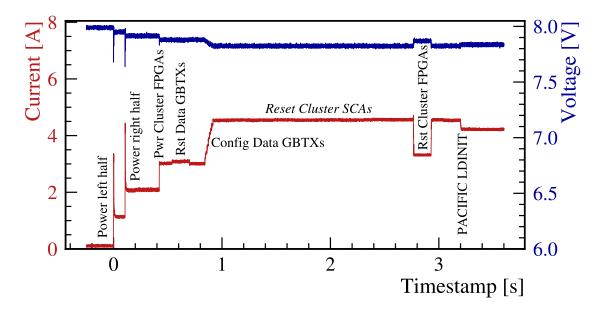

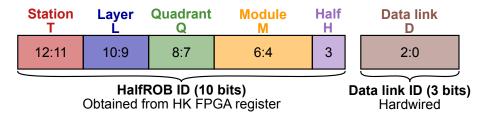

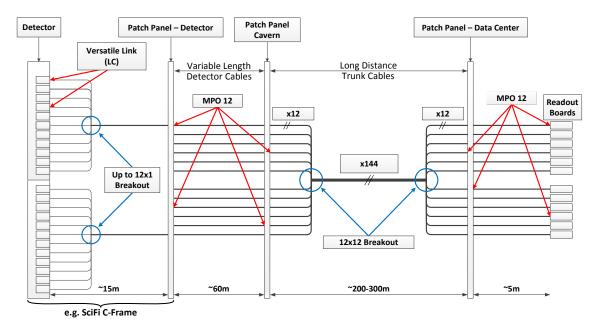

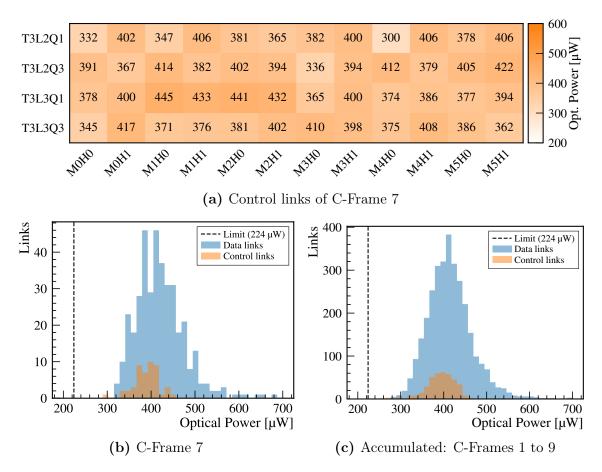

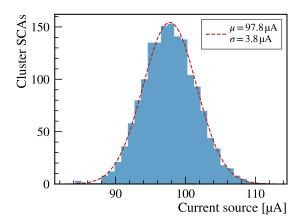

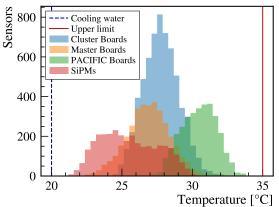

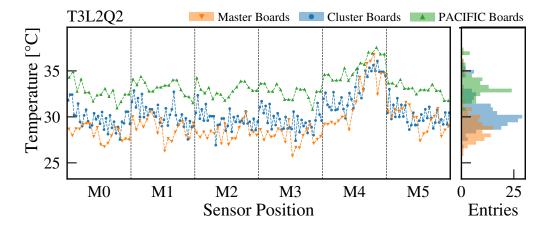

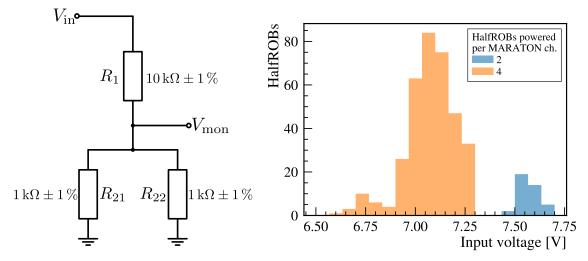

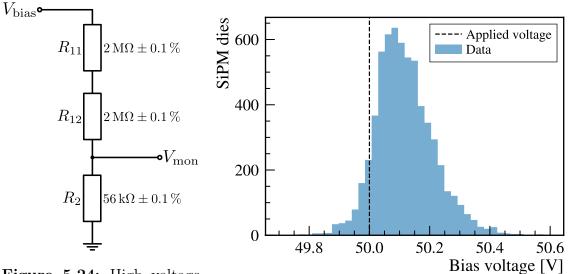

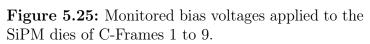

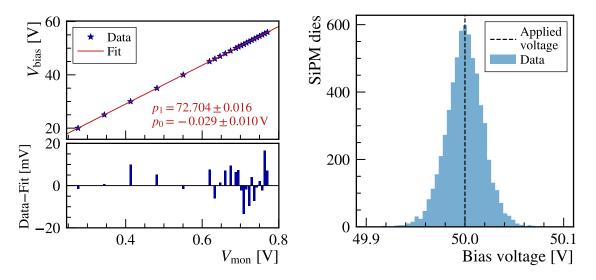

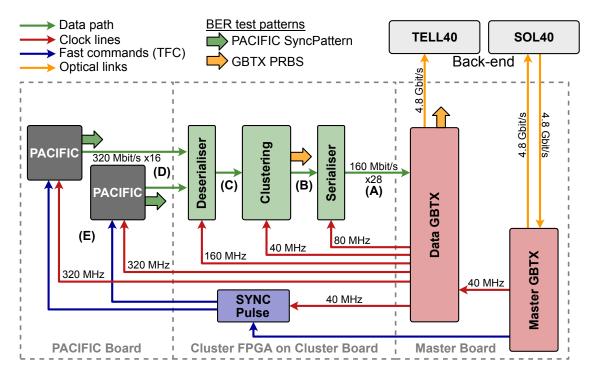

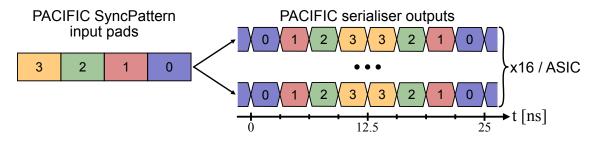

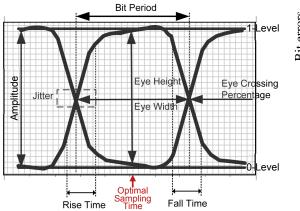

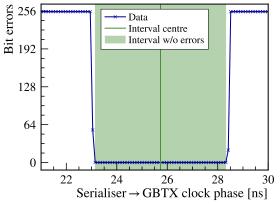

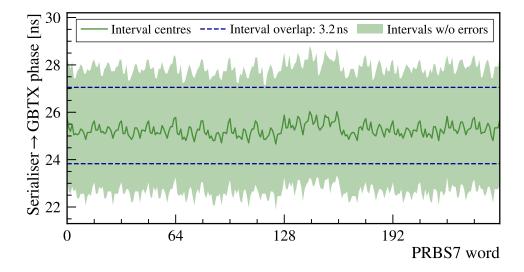

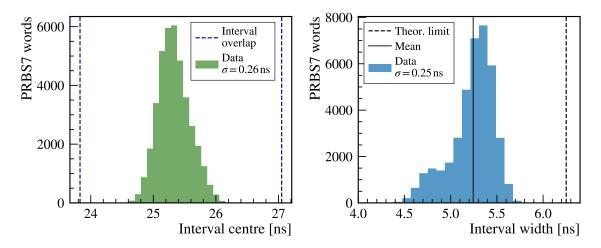

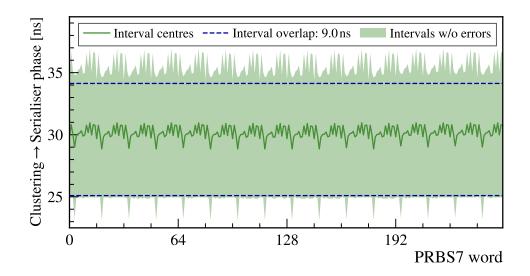

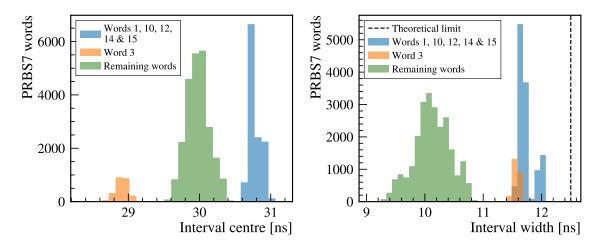

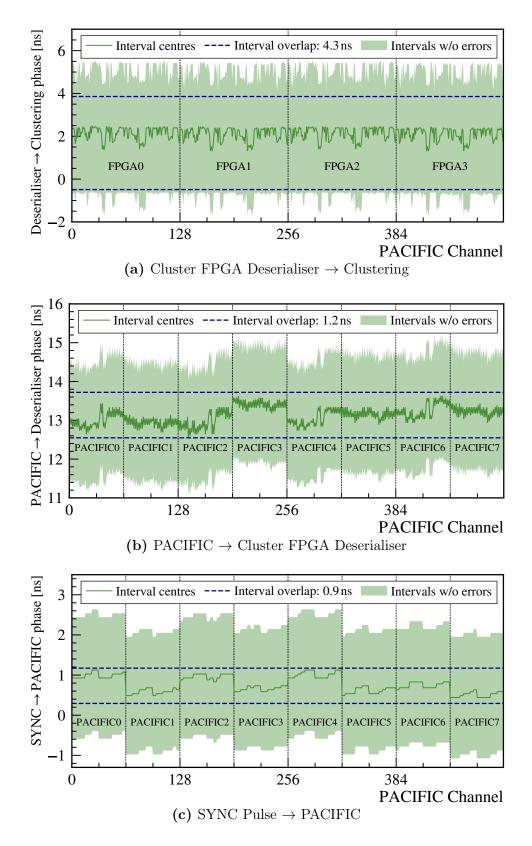

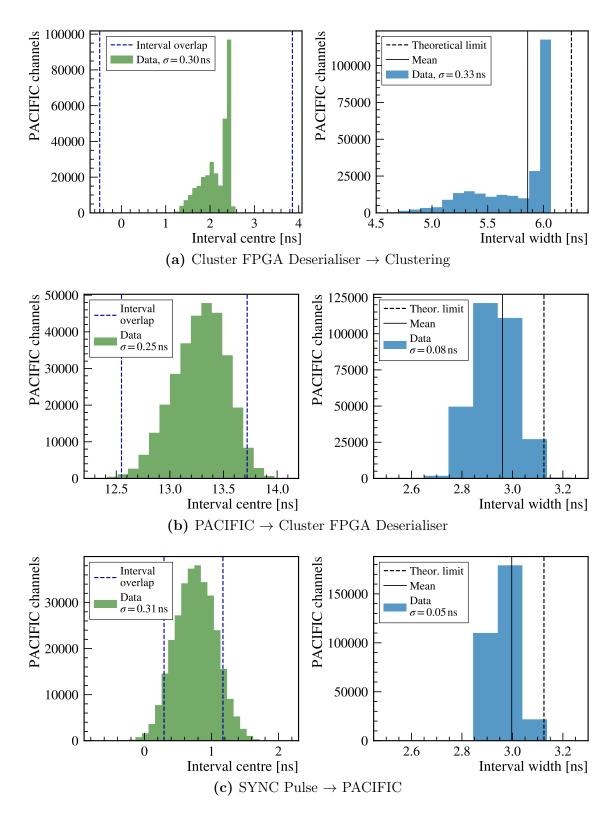

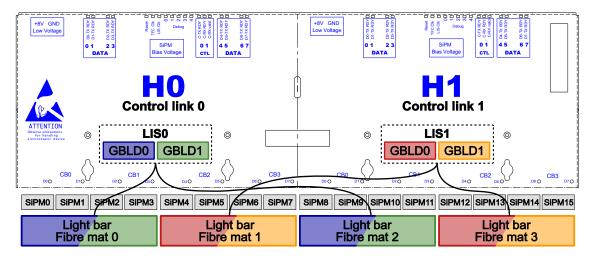

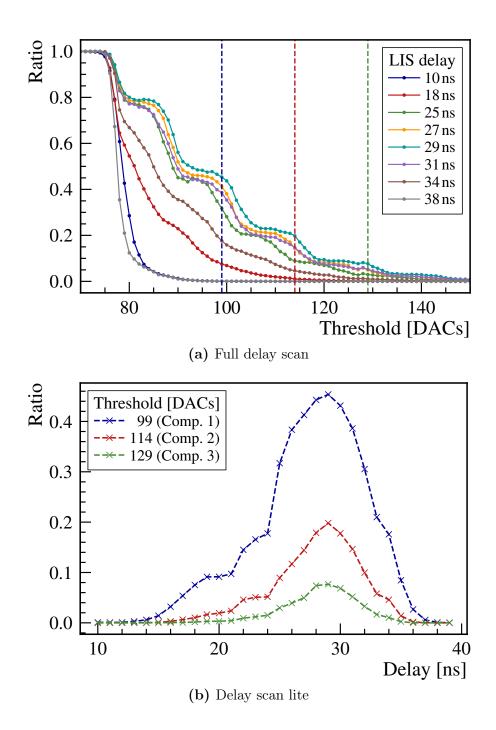

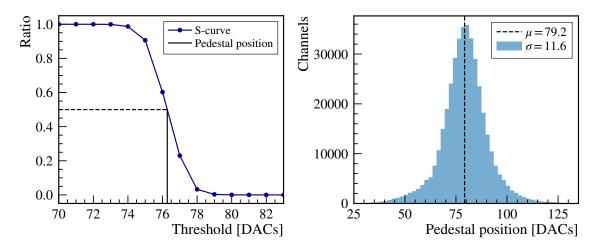

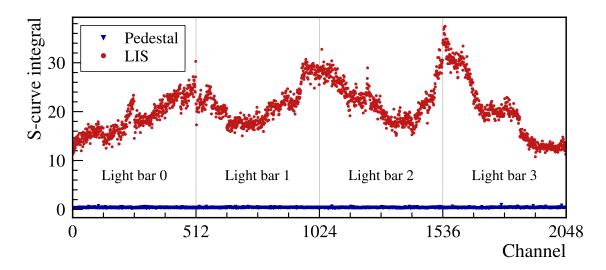

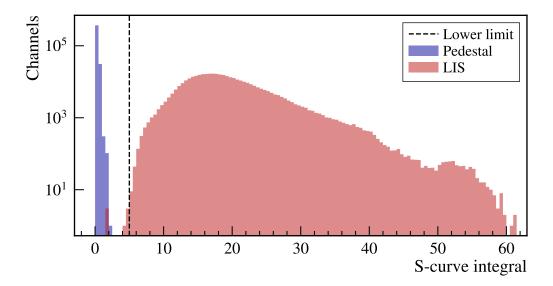

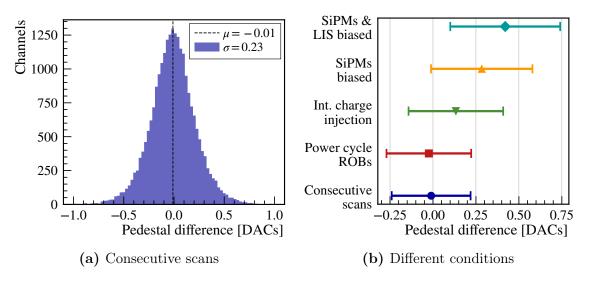

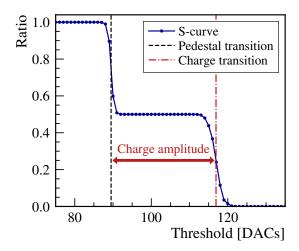

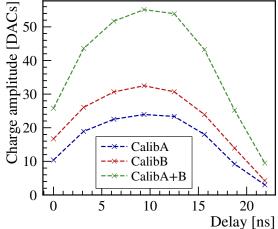

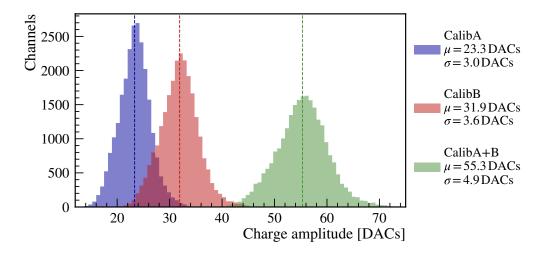

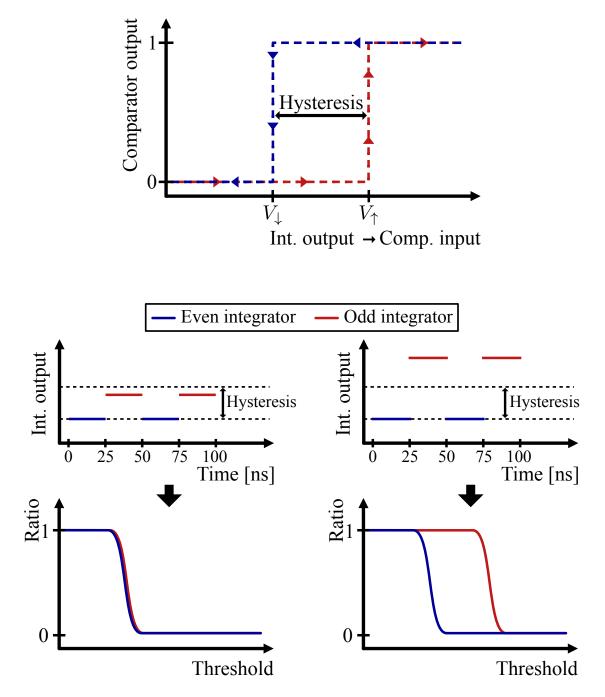

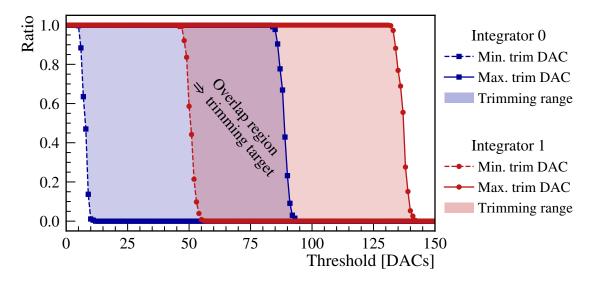

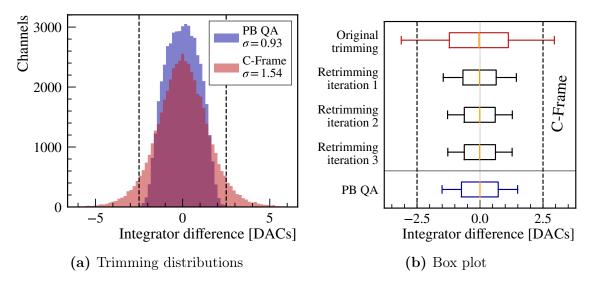

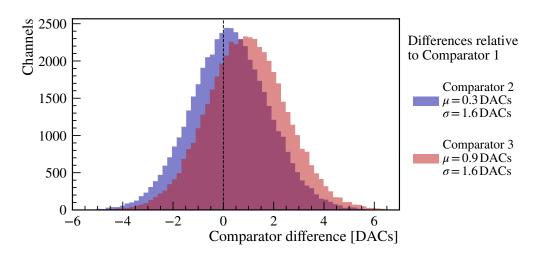

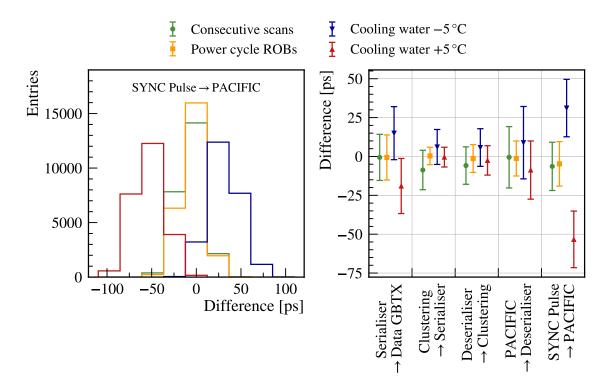

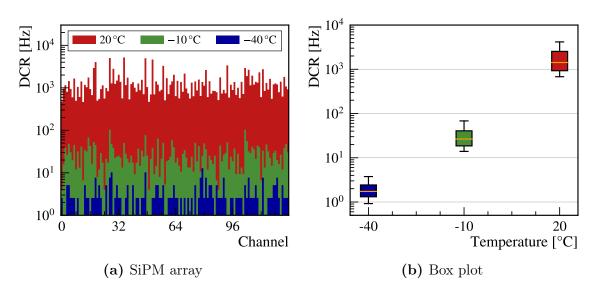

Figure 3.18: Dark count rate (DCR) as a function of the temperature for irradiated H2017 SiPMs at  $\Delta V = 3.5$  V. The coefficient  $T_{1/2}$  that describes the temperature difference at which the DCR is reduced by 1/2 is determined with an exponential fit in the range [-40, -10] °C and indicated by the solid lines. Image adapted from Ref. [61].